**MEMS Reference Shelf**

Reza Ghodssi Pinyen Lin *Editors*

# MEMS Materials and Processes Handbook

MEMS Materials and Processes Handbook

### **MEMS Reference Shelf**

Series Editors:

Stephen D. Senturia Professor of Electrical Engineering, Emeritus Massachusetts Institute of Technology Cambridge, Massachusetts

Antonio J. Ricco Small Satellite Division NASA Ames Research Center Moffett Field, California Roger T. Howe Professor Department of Electrical Engineering Stanford University Stanford, California

For other titles in this series, go to: www.springer.com/series/7724

Reza Ghodssi · Pinyen Lin Editors

## MEMS Materials and Processes Handbook

Editors Reza Ghodssi Department of Electrical and Computer Engineering Institute for Systems Research MEMS Sensors and Actuators Laboratory University of Maryland College Park, Maryland USA ghodssi@umd.edu

Pinyen Lin Touch Micro-system Technology Corp. Taoyuan Taiwan and Walsin Lihwa Corporation Taipei Taiwan pinyen\_lin@alum.mit.edu

ISSN 1936-4407 ISBN 978-0-387-47316-1 DOI 10.1007/978-0-387-47318-5 Springer New York Dordrecht Heidelberg London

Library of Congress Control Number: 2011921730

#### © Springer Science+Business Media, LLC 2011

All rights reserved. This work may not be translated or copied in whole or in part without the written permission of the publisher (Springer Science+Business Media, LLC, 233 Spring Street, New York, NY 10013, USA), except for brief excerpts in connection with reviews or scholarly analysis. Use in connection with any form of information storage and retrieval, electronic adaptation, computer soft-ware, or by similar or dissimilar methodology now known or hereafter developed is forbidden. The use in this publication of trade names, trademarks, service marks, and similar terms, even if they are not identified as such, is not to be taken as an expression of opinion as to whether or not they are subject to proprietary rights.

Printed on acid-free paper

Springer is part of Springer Science+Business Media (www.springer.com)

#### Foreword

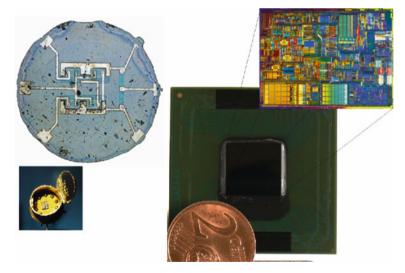

The field that is affectionately known as "MEMS" (an acronym for Micro-Electro-Mechanical Systems) is a descendant of the integrated circuits industry, but a descendent that has developed in ways and directions never anticipated by its parent. Now a highly specialized discipline in its own right, MEMS draws not only on all of conventional microelectronics but also on novel fabrication methods and uses of non-microelectronic materials to create devices that are mechanical, or fluidic, or biochemical, or optical, many without any transistors in sight. The key words are *sensors* and *actuators*, sometimes combined with (or without) microelectronics to create complete microsystems. MEMS devices and microsystems are now found everywhere – in automobiles, in ink-jet printers, in computer games, in mobile telephones, in forensic labs, in factories, in sophisticated instrumentation systems launched into space, in the operating room and in the clinic. The genie is out of the bottle. MEMS devices are everywhere.

Because of this immense diversity, no single book can capture the essence of the entire field. But all MEMS devices represent highly specific answers to two critical questions: "How shall I make it? And from what materials shall I make it?" Processes and materials. Materials and processes. Because these two challenges are common to *all* MEMS devices, it makes sense to gather the wisdom of the least several decades on "how to make it" and "from what materials" into a single datarich, process-detail-rich compendium. That is the *raison d'etre* for this volume, and that is its goal: to document MEMS processes and materials at a sufficient level of detail to be of significant practical use.

I congratulate the co-Editors, Reza Ghodssi and Pinyen Lin, as well as our consulting editors and all of the contributors, for their diligence, persistence, care, and skill in bringing this material to published form, and I invite the MEMS community world-wide to benefit from the knowledge, wisdom and cumulative expertise gathered into these pages.

Brookline, Massachusetts June 2010 Stephen D. Senturia

#### Preface

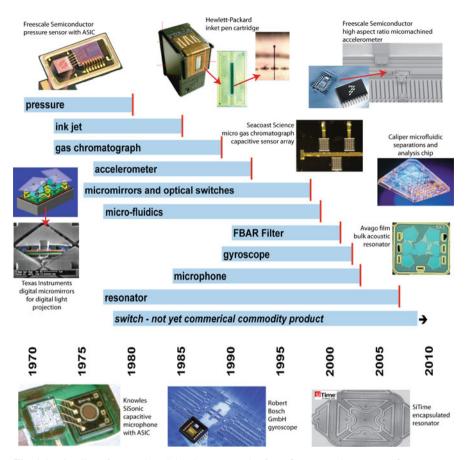

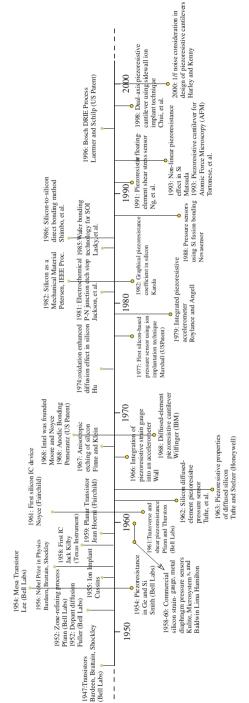

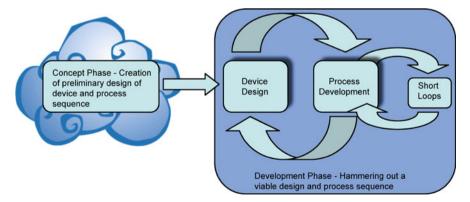

Throughout the relatively short history of microelectromechanical systems (MEMS), there have been numerous advances and inventions directly related to device fabrication. From humble beginnings using borrowed and modified IC fabrication techniques to current MEMS-specific tools such as deep reactive ion etching (DRIE) using inductively coupled plasma (ICP) sources, MEMS researchers have continually advanced and augmented the capabilities of wafer-based fabrication technologies. These advances have been instrumental in the demonstration of new devices and applications – Texas Instruments' Digital Micromirror Device, the MIT microturbine, Analog Devices' accelerometers – and even in the creation of new fields of research and development: bioMEMS, microfluidic devices, and optical MEMS.

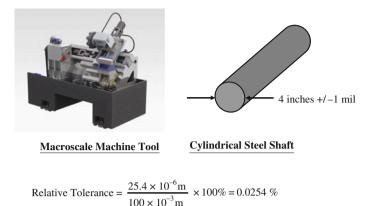

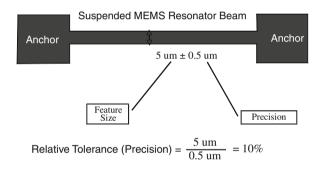

To date, a number of books have been written about these new fabrication technologies and materials in general, but discussion of their relationship to MEMS design has been minimal. As a particularly diverse and multidisciplinary area of research, the field of MEMS offers a vastly different set of challenges relative to typical IC fabrication and design. Much effort is often focused on characterization runs and developing in-house recipes and specific processes to develop and manufacture MEMS structures, each time at the risk of wasting research efforts and "reinventing the wheel." A wealth of knowledge exists in the MEMS community, but much of this expertise is most readily accessed by informal, nonmethodological means such as discussions with colleagues at conferences. The authors of this book have observed an unnecessarily steep learning curve for the development of common MEMS processes, and believe the time spent traversing this curve would be better spent brainstorming new ideas and uncovering new applications. This book was conceived and born of this belief.

A fundamental and comprehensive MEMS-focused reference book will be an important asset for current and future research scientists and engineers. It was decided early in the brainstorming sessions for this book to include *materials* as well as *processes* in the discussion, as MEMS utilizes a wide variety of each in common applications. We intend this book to provide the reader with the basics of MEMS materials and processes, but beyond this goal, we intend for it to give practical insight into the workings and standard procedures carried out in research labs

and production facilities on a daily basis. To this end, each chapter has an extended section with case studies, giving step-by-step examples and recipes prepared by experts in industry and academia. Particularly, the effect of processing conditions on material properties are covered where applicable, illustrating the interdependence and multidisciplinary nature of MEMS fabrication. The chapters are meant to be a springboard of sorts, providing basic information about each topic, with a large number of classic and contemporary literature references to provide in-depth knowledge. Ultimately, it is our goal to provide a useful design reference volume for the seasoned researcher and the MEMS newcomer alike. We hope this book consolidates important information for readers and thereby spurs the creation of many new devices and processes.

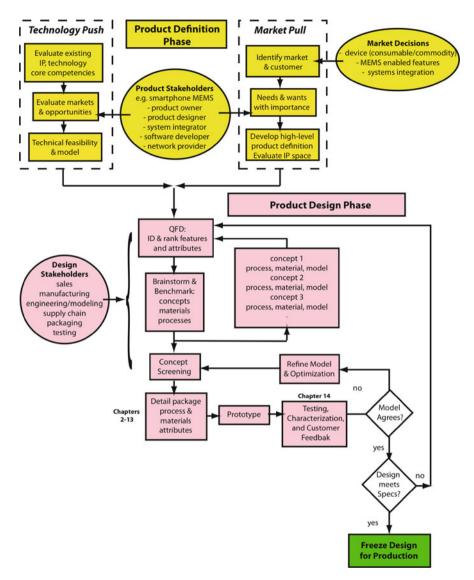

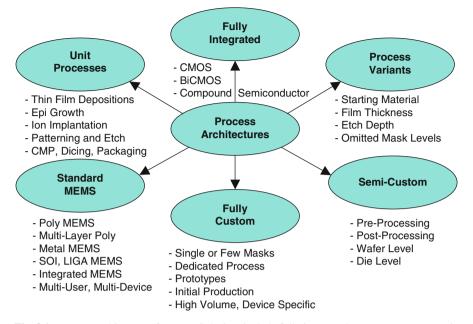

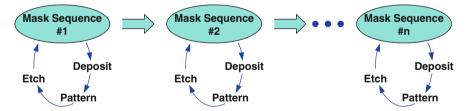

MEMS devices are essentially microsystems that have structures and empty space built together. The authors of this book view the materials and processes as the fundamental building blocks for making those structures and empty spaces. Keeping this in mind, the book is divided into two main sections: Chapters 2, 3, 4, 5, and 6 covering materials and Chapters 7, 8, 9, 10, 11, 12, and 13 covering fabrication techniques. These two general thrusts are bookended by Chapter 1, which discusses general MEMS design, and Chapter 14, which deals with MEMS process integration.

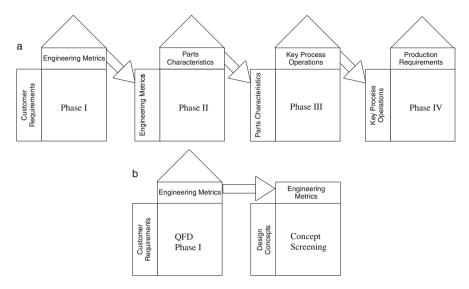

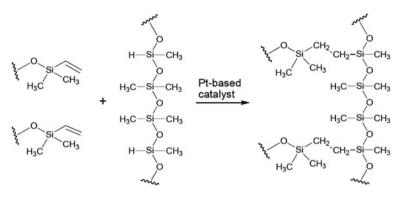

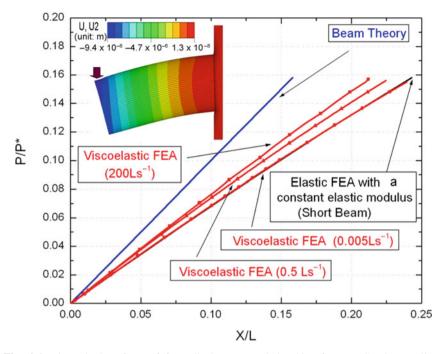

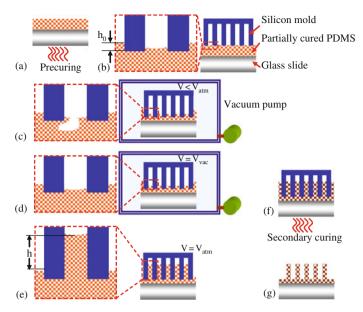

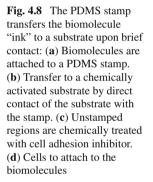

Chapter 1 provides a basic framework for the design of MEMS systems and processes, which we highly recommend reading before diving into the materials and process sections of the book. Chapter 2 presents an overview of the recipes and methods used in the deposition of semiconductor and dielectric thin-films, particularly those most commonly used in the fabrication of MEMS. The basics here include chemical vapor deposition, epitaxy, physical vapor deposition, atomic layer deposition, and spin-on techniques. Additive processes for depositing metal films are discussed in detail in Chapter 3, where particular attention is paid to thick metal deposition with significant coverage devoted to electrochemical and electroless plating processes that are often required for MEMS fabrication. The entirety of Chapter 4 is devoted to the use of polymeric materials for MEMS. Polymers, such as polydimethylsiloxane (PDMS), are important materials for a vast array of devices, as encapsulants for tactile sensors and as an integral enabling technology for the emerging field of bioMEMS. The piezoelectric films detailed in Chapter 5 are an important part of MEMS technology, serving as both sensor and actuator elements. The basic properties of these materials and the physics of operation are described in detail as well as practical deposition and fabrication methods. Chapter 6 focuses on the fabrication and integration of shape memory alloy (SMA) materials, which provide high-force and high-displacement actuator mechanisms for MEMS.

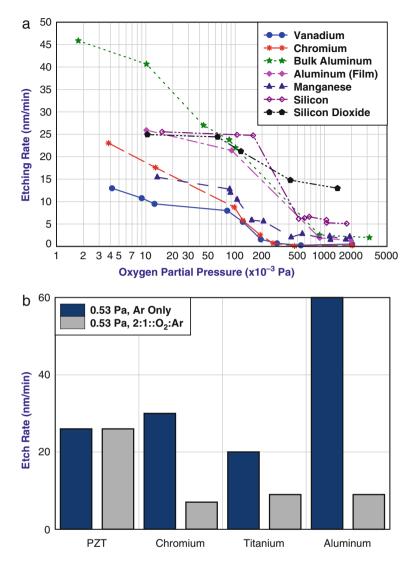

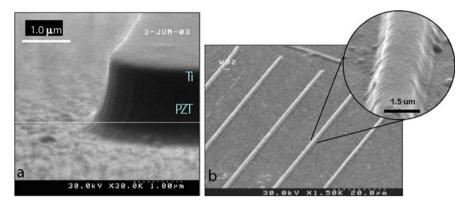

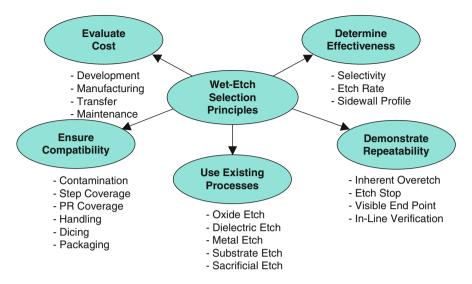

Chapter 7 begins the section on processing of materials for MEMS applications by covering the very important area of dry etching methods (including DRIE), particularly the influence of different parameters on the etch recipe development process. Complementing the coverage of dry etching, wet etching processes for MEMS micromachining are covered in Chapter 8 with a comprehensive recipe and reference list included in this chapter to aid in finding etch rates and etch selectivities for a wide range of materials from silicon to III–V compound semiconductors.

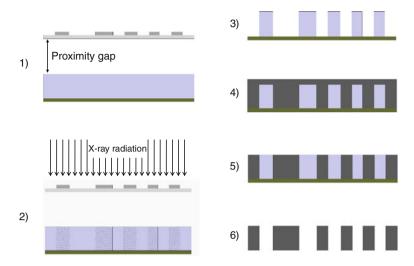

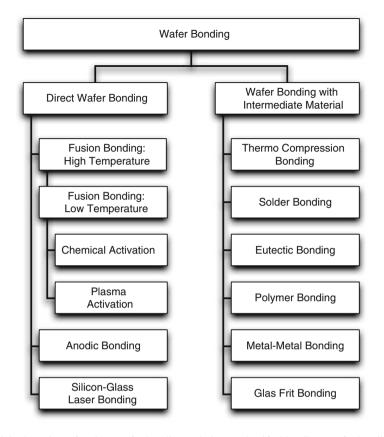

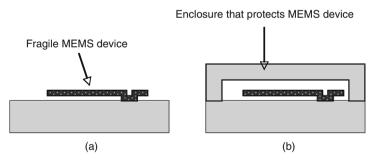

Chapter 9 describes the technology of lithography and related techniques, covering traditional contact lithography, projection and X-ray lithography, and more exotic direct-write and printing lithographic techniques. Doping processes typical in and for MEMS applications for electrical purposes and etching control are reviewed in Chapter 10, along with diagnostic techniques for these methods. Wafer bonding, a crucial fabrication technique for silicon MEMS encapsulation and structure fabrication, is covered in detail in Chapter 11 with emphasis placed on direct and intermediate layer bonding methods.

Chapter 12 discusses the still-evolving field of MEMS packaging, pointing out differences with current microcircuit packaging techniques; this chapter in particular highlights how MEMS devices present very unique challenges as compared to traditional microcircuits. Surface treatments for MEMS devices are discussed in Chapter 13, covering antistiction and planarization coatings, functionalization of surfaces for biological and optical applications, and chemical mechanical polishing (CMP). Chapter 14 concludes the book with a discussion of the integration of any number of the above processes and materials into a compatible and efficient process flow, referred to here as *process integration*. The final chapter also discusses economic and practical aspects of process integration, citing some commercially successful examples of MEMS devices.

This reference volume would not have been possible without the help of many of our colleagues in the MEMS fields, from both academia and industry. We would like to extend words of thanks and gratitude to Stephen (Steve) Senturia for providing the vision, support, and guidance to our team over the past five years in navigating the completion of the chapters and for reviewing them diligently, and to the Series Associate Editors Roger Howe and Antonio (Tony) Ricco for carefully reviewing the chapters, providing helpful comments, and for recommending prospective contributing authors. We thank Steven (Steve) Elliot, from Springer, for his patience in dealing with thirty-five unique and independent experts, and his persistence in contacting each of us in order to develop the logistics for the book publishing process. Last but not least, we acknowledge all thirty-five contributing authors, who selflessly gave time, expertise, effort, and creativity to make this book a one-of-a-kind contribution to the current and future MEMS community, including industry and government professionals, academic faculty and staff, and students.

The idea for this book was born at the *Transducers 2005 Conference* in Seoul, South Korea, and it was finalized and finished at *The Hilton Head 2010 Workshop* on Hilton Head Island, South Carolina. The five years of cooperative activity that culminated in this handbook prove that great ideas can become reality when colleagues work collaboratively to achieve a common goal. This message, which we have tried to convey by writing this book, is what the greater MEMS community is all about.

College Park, Maryland Taoyuan, Taiwan Reza Ghodssi Pinyen Lin

#### Contents

| 1 | The l | MEMS D   | esign Process                           | 1  |

|---|-------|----------|-----------------------------------------|----|

|   | 1.1   |          | ction                                   | 1  |

|   |       | 1.1.1    | Design Process                          | 5  |

|   | 1.2   | Design I | Methods for MEMS                        | 7  |

|   |       | 1.2.1    | History of Design Methodologies         | 7  |

|   |       | 1.2.2    | Structured Design Methods for MEMS      | 8  |

|   | 1.3   | Brainsto | orming                                  | 9  |

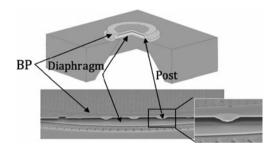

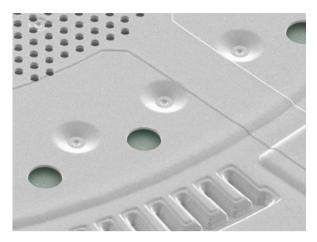

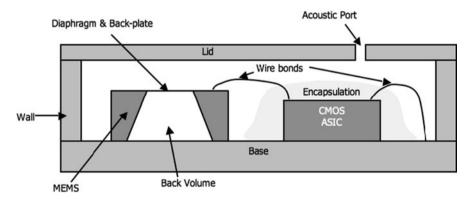

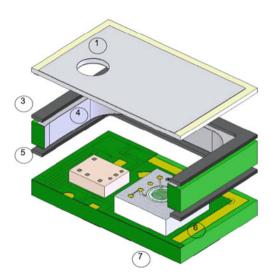

|   | 1.4   | Microph  | none Case Studies                       | 10 |

|   |       | 1.4.1    | Microphone Background                   | 10 |

|   |       | 1.4.2    | The Avago Story                         | 11 |

|   |       |          | 1.4.2.1 Design Process and Methods      | 11 |

|   |       | 1.4.3    | The Knowles Story                       | 20 |

|   |       | 1.4.4    | Summary of Key Concepts                 | 22 |

|   | 1.5   | Material | ls and Process Selection                | 23 |

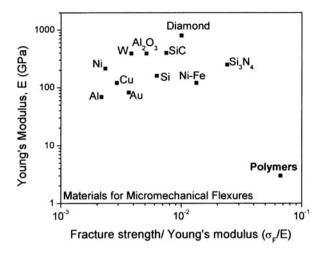

|   |       | 1.5.1    | Materials Selection                     | 23 |

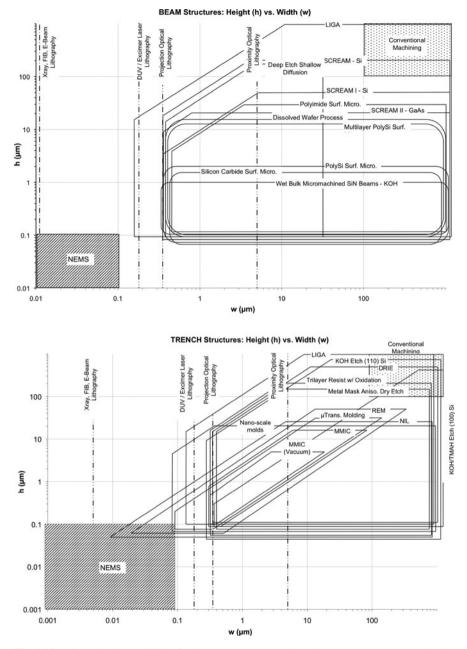

|   |       | 1.5.2    | Process Selection                       | 23 |

|   | 1.6   | Evaluate | e Concepts                              | 30 |

|   |       | 1.6.1    | Modeling                                | 30 |

|   | 1.7   | Optimiz  | ation and Other Design Methods          | 31 |

|   |       | 1.7.1    | Design Optimization                     | 31 |

|   |       | 1.7.2    | Uncertainty Analysis                    | 31 |

|   |       | 1.7.3    | FMEA                                    | 31 |

|   |       | 1.7.4    | Design Method Timing                    | 32 |

|   | 1.8   | Summar   | ry                                      | 33 |

|   | Refer | ences .  |                                         | 33 |

| • |       |          |                                         |    |

| 2 |       |          | esses for Semiconductors and Dielectric | 27 |

|   |       |          |                                         | 37 |

|   | 2.1   |          | W                                       | 37 |

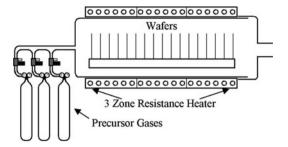

|   | 2.2   |          | Conversion                              | 38 |

|   |       | 2.2.1    | Process Overview                        | 38 |

|     | 2.2.2 |          | roperties and Process Selection<br>Thermal Oxidation of Silicon | 43       |

|-----|-------|----------|-----------------------------------------------------------------|----------|

|     | 2.2.3 |          |                                                                 | 45       |

| 2.3 |       |          |                                                                 | 45       |

| 2.5 |       |          | eposition                                                       | 45<br>45 |

|     | 2.3.1 |          |                                                                 |          |

|     |       | 2.3.1.1  | Introduction                                                    | 45       |

|     |       | 2.3.1.2  | Low Pressure Chemical Vapor                                     | 47       |

|     |       |          | Deposition                                                      | 47       |

|     |       | 2.3.1.3  | Plasma-Enhanced Chemical                                        | -        |

|     |       |          | Vapor Deposition                                                | 50       |

|     |       | 2.3.1.4  | Atmospheric Pressure Chemical                                   |          |

|     |       |          | Vapor Deposition                                                | 52       |

|     |       | 2.3.1.5  | Hot Filament Chemical Vapor                                     |          |

|     |       |          | Deposition                                                      | 53       |

|     |       | 2.3.1.6  | Microwave Plasma Chemical                                       |          |

|     |       |          | Vapor Deposition                                                | 53       |

|     | 2.3.2 | LPCVD P  | olycrystalline Silicon                                          | 53       |

|     |       | 2.3.2.1  | Material Properties and Process                                 |          |

|     |       |          | Generalities                                                    | 53       |

|     |       | 2.3.2.2  | Process Selection Guidelines                                    | 55       |

|     |       | 2.3.2.3  | Case Studies                                                    | 56       |

|     | 2.3.3 | LPCVD Si | ilicon Dioxide                                                  | 65       |

|     |       | 2.3.3.1  | Material Properties and Process                                 |          |

|     |       |          | Generalities                                                    | 65       |

|     |       | 2.3.3.2  | Process Selection Guidelines                                    | 66       |

|     |       | 2.3.3.3  | Case Studies                                                    | 67       |

|     | 2.3.4 |          | ilicon Nitride                                                  | 69       |

|     | 2.5.1 | 2.3.4.1  | Material Properties and Process                                 | 0)       |

|     |       | 2.3.1.1  | Generalities                                                    | 69       |

|     |       | 2.3.4.2  | Process Selection Guidelines                                    | 70       |

|     |       | 2.3.4.3  | Case Studies                                                    | 70       |

|     | 2.3.5 |          | olycrystalline SiGe and Ge                                      | 73       |

|     | 2.3.3 | 2.3.5.1  |                                                                 | 15       |

|     |       | 2.3.3.1  | Material Properties and Process                                 | 73       |

|     |       | 0 2 5 0  | Generalities                                                    |          |

|     | 0.0.6 | 2.3.5.2  | Process Selection Guidelines                                    | 75       |

|     | 2.3.6 |          | olycrystalline Silicon Carbide                                  | 75       |

|     |       | 2.3.6.1  | Material Properties and Process                                 |          |

|     |       |          | Generalities                                                    | 75       |

|     |       | 2.3.6.2  | Process Selection Guidelines                                    | 79       |

|     |       | 2.3.6.3  | Case Studies                                                    | 79       |

|     | 2.3.7 | LPCVD D  | iamond                                                          | 85       |

|     |       | 2.3.7.1  | Material Properties and Process                                 |          |

|     |       |          | Generalities                                                    | 85       |

|     |       | 2.3.7.2  | Process Selection Guidelines                                    | 86       |

|     |       | 2.3.7.3  | Case Studies                                                    | 86       |

|     | 2.3.8   | APCVD Po | olycrystalline Silicon Carbide                  | 89  |

|-----|---------|----------|-------------------------------------------------|-----|

|     |         | 2.3.8.1  | Material Properties and Process                 |     |

|     |         |          | Generalities                                    | 89  |

|     |         | 2.3.8.2  | Process Selection Guidelines                    | 89  |

|     | 2.3.9   | PECVD Si | licon                                           | 89  |

|     |         | 2.3.9.1  | Material Properties and Process                 |     |

|     |         |          | Generalities                                    | 89  |

|     |         | 2.3.9.2  | Process Selection Guidelines                    | 91  |

|     | 2.3.10  | PECVD Si | licon Dioxide                                   | 91  |

|     |         | 2.3.10.1 | Material Properties and Process                 |     |

|     |         |          | Generalities                                    | 91  |

|     |         | 2.3.10.2 | Process Selection Guidelines                    | 91  |

|     | 2.3.11  | PECVD Si | licon Nitride                                   | 95  |

|     |         | 2.3.11.1 | Material Properties and Process                 |     |

|     |         |          | Generalities                                    | 95  |

|     |         | 2.3.11.2 | Process Selection Guidelines                    | 95  |

|     | 2.3.12  |          | licon Germanium                                 | 95  |

|     | 210112  | 2.3.12.1 | Material Properties and Process                 | 20  |

|     |         | 21011211 | Generalities                                    | 95  |

|     |         | 2.3.12.2 | Process Selection Guidelines                    | 97  |

|     |         | 2.3.12.3 | Case Studies                                    | 97  |

|     | 2.3.13  |          | licon Carbide                                   | 101 |

|     | 2.5.15  | 2.3.13.1 | Material Properties and Process                 | 101 |

|     |         | 2.3.13.1 | Generalities                                    | 101 |

|     |         | 2.3.13.2 | Process Selection Guidelines                    | 101 |

|     |         | 2.3.13.2 | Case Studies                                    | 102 |

|     | 2.3.14  |          | arbon-Based Films                               | 102 |

|     | 2.3.14  | 2.3.14.1 | Material Properties and Process                 | 104 |

|     |         | 2.3.14.1 | Generalities                                    | 104 |

|     |         | 2.3.14.2 | Process Selection Guidelines                    | 104 |

| 2.4 | Enitovy |          |                                                 | 104 |

| 2.4 | 2.4.1   |          | rerviews                                        | 105 |

|     | 2.4.1   |          | licon                                           | 105 |

|     | 2.4.2   | 2.4.2.1  |                                                 | 100 |

|     |         | 2.4.2.1  | Material Properties and Process<br>Generalities | 106 |

|     |         | 2422     |                                                 | 106 |

|     |         | 2.4.2.2  | Process Selection Guidelines                    | 107 |

|     | 2.4.2   | 2.4.2.3  | Case Studies                                    | 107 |

|     | 2.4.3   | -        | ilicon Carbide                                  | 108 |

|     |         | 2.4.3.1  | Material Properties and Process                 | 100 |

|     |         | 2 4 2 2  | Generalities                                    | 108 |

|     |         | 2.4.3.2  | Process Selection Guidelines                    | 109 |

|     | 2.4.4   | 2.4.3.3  | Case Studies                                    | 109 |

|     | 2.4.4   |          | rials and Gallium Nitride                       | 111 |

|     |         | 2.4.4.1  | Material Properties and Process                 |     |

|     |         |          | Generalities                                    | 111 |

|   |       |            | 2.4.4.2     | Process Selection Guidelines 11                 | 1 |

|---|-------|------------|-------------|-------------------------------------------------|---|

|   |       |            | 2.4.4.3     | Case Studies                                    | 1 |

|   | 2.5   | Physical   | Vapor Dep   | osition                                         | 4 |

|   |       | 2.5.1      | Process Ov  | verviews                                        | 4 |

|   |       | 2.5.2      | Sputter-De  | posited Si                                      | 5 |

|   |       |            | 2.5.2.1     | Material Properties and Process                 |   |

|   |       |            |             | Generalities                                    | 5 |

|   |       |            | 2.5.2.2     | Process Selection Guidelines 11                 | 6 |

|   |       | 2.5.3      | Sputter-De  | posited SiC                                     | 6 |

|   |       | 2.5.4      |             | posited $SiO_2$                                 | 7 |

|   |       | 2.5.5      | Sputter-De  | posited Diamondlike Carbon 11                   | 8 |

|   |       | 2.5.6      |             | ms Deposited by Pulsed Laser Deposition . 11    | 8 |

|   | 2.6   | Atomic     | Layer Depo  | sition                                          | 9 |

|   |       | 2.6.1      | Process Ov  | verview                                         | 9 |

|   |       | 2.6.2      | Process Se  | lection Guidelines and Material Properties . 12 | 0 |

|   | 2.7   | Spin-On    | Films       |                                                 | 1 |

|   | Refer | ences .    |             |                                                 | 3 |

| 3 | Addi  | tive Proce | esses for M | <b>etals</b>                                    | 7 |

| 0 | 3.1   |            |             | 13                                              |   |

|   | 5.1   | 3.1.1      |             |                                                 |   |

|   |       |            |             | 13 Tradeoffs                                    |   |

|   | 3.2   |            |             | osition                                         |   |

|   | 5.2   |            | 1 1         | n                                               |   |

|   |       | 0.211      | 3.2.1.1     | Thermal Evaporation                             |   |

|   |       |            | 3.2.1.2     | E-Beam Evaporation                              |   |

|   |       |            | 3.2.1.3     | Issues with Alloys                              |   |

|   |       | 3.2.2      | Sputtering  |                                                 |   |

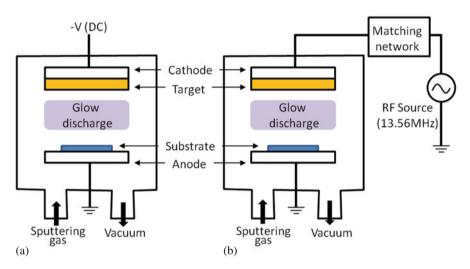

|   |       | 0.2.12     | 3.2.2.1     | DC Sputtering                                   |   |

|   |       |            | 3.2.2.2     | RF Sputtering                                   |   |

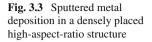

|   |       |            | 3.2.2.3     | Step Coverage                                   |   |

|   |       |            | 3.2.2.4     | Other Issues in Sputtering                      |   |

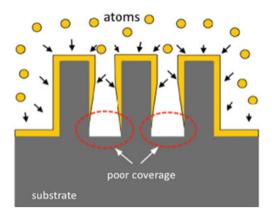

|   |       | 3.2.3      | Pulsed Las  | er Deposition                                   |   |

|   | 3.3   |            |             | position                                        | 7 |

|   |       |            |             | ing                                             | 7 |

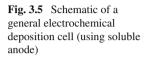

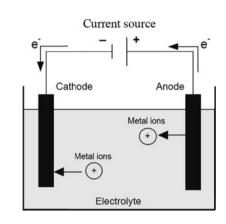

|   |       |            | 3.3.1.1     | Electrochemical Reactions                       | 7 |

|   |       |            | 3.3.1.2     | Deposition Process                              | 9 |

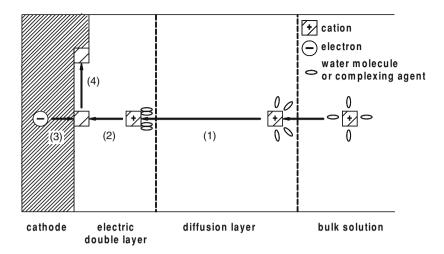

|   |       |            | 3.3.1.3     | Overpotential 15                                | 2 |

|   |       |            | 3.3.1.4     | Bath Composition                                | 3 |

|   |       |            | 3.3.1.5     | Current Waveform                                |   |

|   |       |            | 3.3.1.6     | Equipment                                       |   |

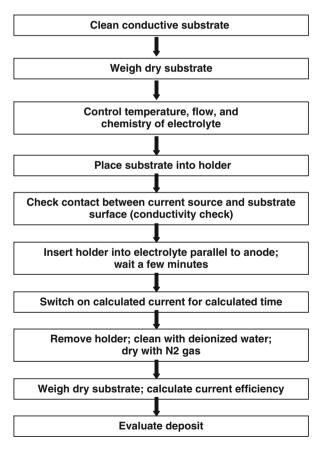

|   |       |            | 3.3.1.7     | Process Flow                                    |   |

|   |       |            | 3.3.1.8     | Nickel                                          |   |

|   |       |            | 3.3.1.9     | Copper                                          |   |

|   |       |            | 3.3.1.10    | Gold                                            | 9 |

|   |       |        | 3.3.1.11 Nickel Alloys                          | 51 |

|---|-------|--------|-------------------------------------------------|----|

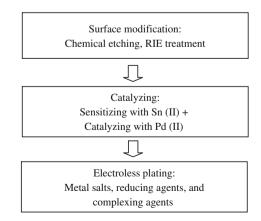

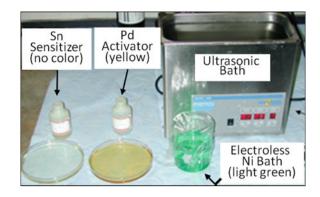

|   |       | 3.3.2  | Electroless Plating                             | 52 |

|   |       |        | 3.3.2.1 Nickel                                  | 54 |

|   |       |        | 3.3.2.2 Copper                                  | 66 |

|   |       |        | 3.3.2.3 Gold                                    | 58 |

|   |       | 3.3.3  | Comparison of Electroplating and Electroless    |    |

|   |       |        | Plating                                         | 59 |

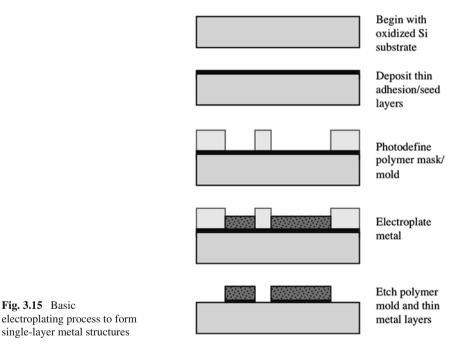

|   | 3.4   | LIGA a | and UV-LIGA Processes                           |    |

|   |       | 3.4.1  | Process Explanation                             |    |

|   |       | 3.4.2  | Electroplating in LIGA and UV-LIGA              |    |

|   |       | 01112  | Microstructures                                 | 71 |

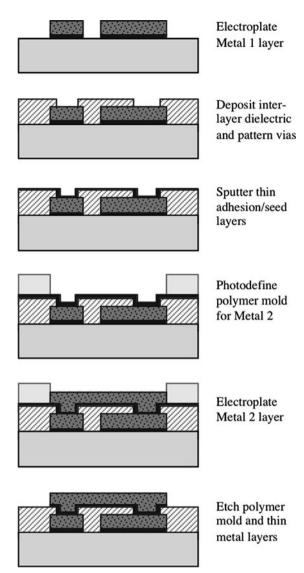

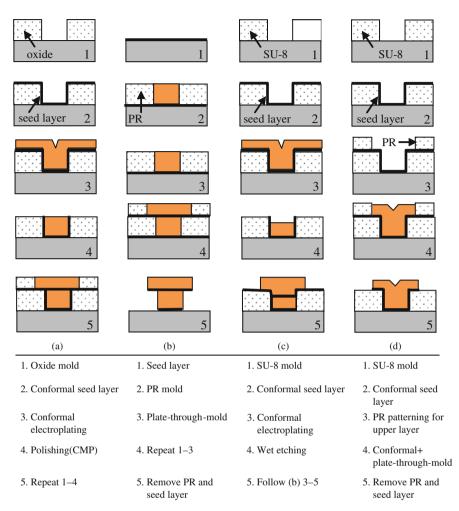

|   |       | 3.4.3  | Multilevel Metal Structures                     |    |

|   | 3.5   |        | als Properties and Process Selection Guidelines | 5  |

|   | 5.5   |        | tals                                            | 79 |

|   |       | 3.5.1  | Adhesion                                        |    |

|   |       | 3.5.2  | Electrical Properties                           |    |

|   |       | 3.5.3  | Mechanical Properties                           |    |

|   |       | 3.5.4  | Thermal Properties                              |    |

|   |       | 3.5.5  | Magnetic Properties                             |    |

|   | Pafar |        |                                                 |    |

|   |       |        |                                                 | 0  |

| 4 | Addi  |        | cesses for Polymeric Materials                  | )3 |

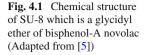

|   | 4.1   | SU-8 . | 19                                              |    |

|   |       | 4.1.1  | Material Properties                             |    |

|   |       | 4.1.2  | Processing Variations                           | )6 |

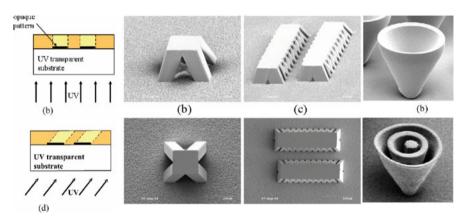

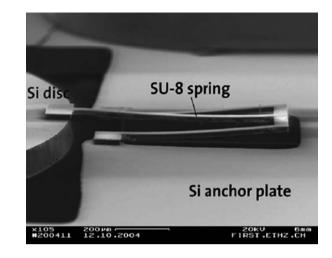

|   |       |        | 4.1.2.1 Partial Exposure                        | )6 |

|   |       |        | 4.1.2.2 Direct Writing                          | 97 |

|   |       |        | 4.1.2.3 Removal of SU-8                         | 97 |

|   |       |        | 4.1.2.4 Release of SU-8                         | 98 |

|   |       |        | 4.1.2.5 Bonding                                 | 98 |

|   |       |        | 4.1.2.6 Transfer                                | 99 |

|   |       |        | 4.1.2.7 SU-8 as an Etch Mask                    | 99 |

|   |       | 4.1.3  | Lessons Learned                                 | 99 |

|   |       | 4.1.4  | Examples of SU-8 Application                    | )1 |

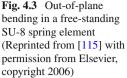

|   | 4.2   | PDMS   |                                                 | )1 |

|   |       | 4.2.1  | Material Properties                             | )2 |

|   |       | 4.2.2  | Processing Techniques                           | )3 |

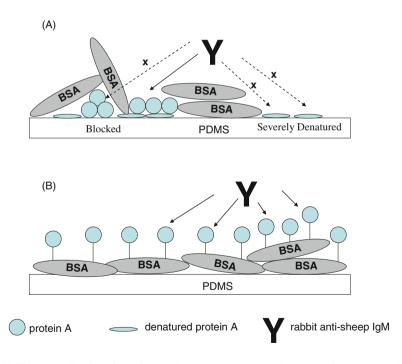

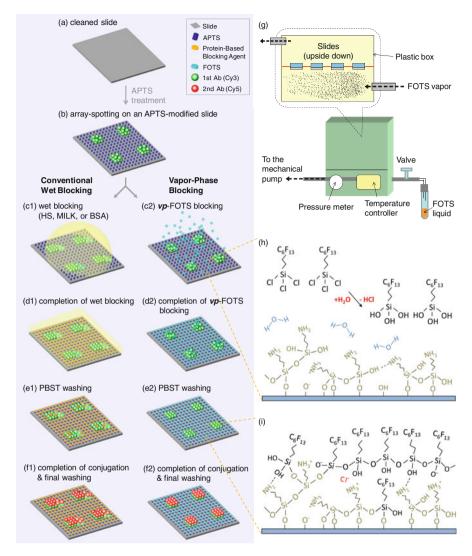

|   |       | 4.2.3  | Biological Application Guide                    | )5 |

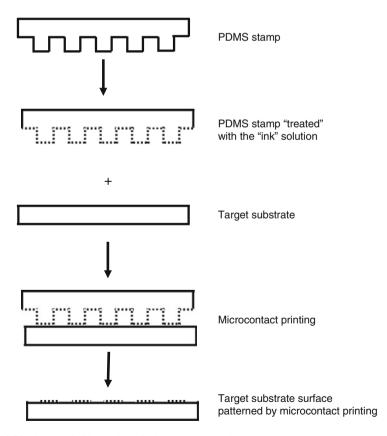

|   |       |        | 4.2.3.1 Stamp Material for Protein              |    |

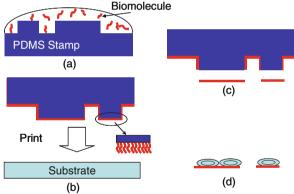

|   |       |        | Transfer: Microcontact Printing 20              | )6 |

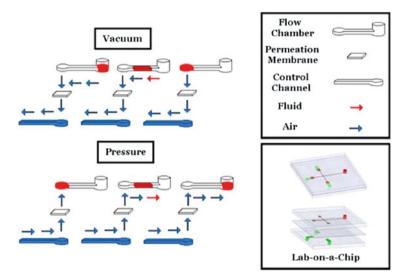

|   |       |        | 4.2.3.2 Microfluidic Devices                    | )6 |

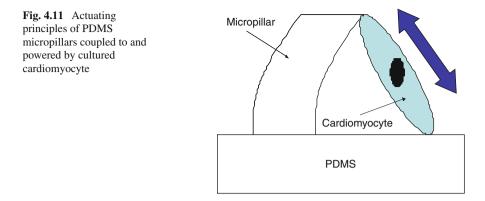

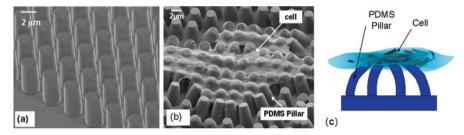

|   |       | 4.2.4  | Case Study                                      |    |

|   | 4.3   |        | ide                                             |    |

|   |       | 4.3.1  | Material Properties                             |    |

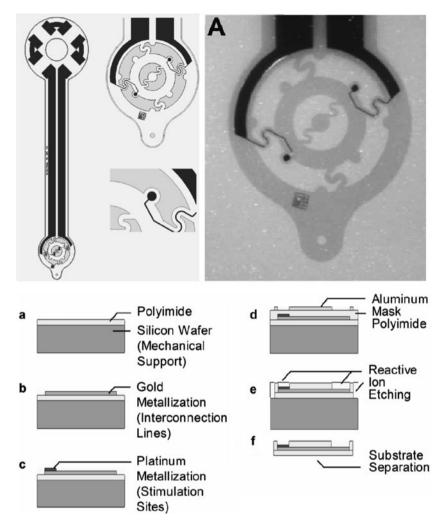

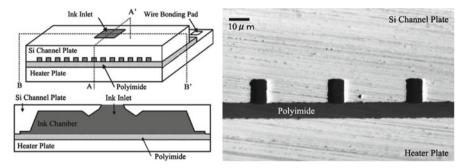

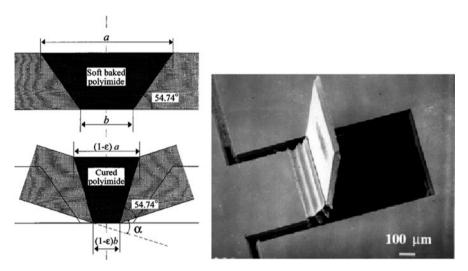

|   |       | 4.3.2  | Processing Variations                           |    |

|   |       |        |                                                 | -  |

|     |        | 4.3.2.1    | Removal of Polyimide           | 213        |

|-----|--------|------------|--------------------------------|------------|

|     |        | 4.3.2.2    | Release of Polyimide           | 213        |

|     |        | 4.3.2.3    | Bonding                        | 215        |

|     | 4.3.3  | Lessons L  |                                | 215        |

|     | 4.3.4  | Case Stud  | у                              | 216        |

| 4.4 | Hydro  |            | -                              | 216        |

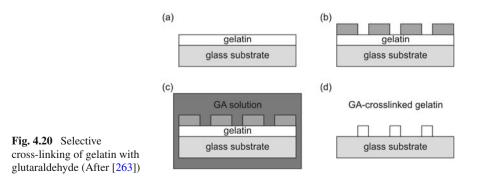

|     | 4.4.1  | Gelatin .  |                                | 216        |

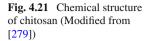

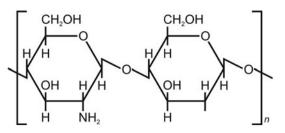

|     | 4.4.2  | Chitosan   |                                | 218        |

|     | 4.4.3  | Polyethyle | ene Glycol                     | 220        |

|     | 4.4.4  |            | •                              | 222        |

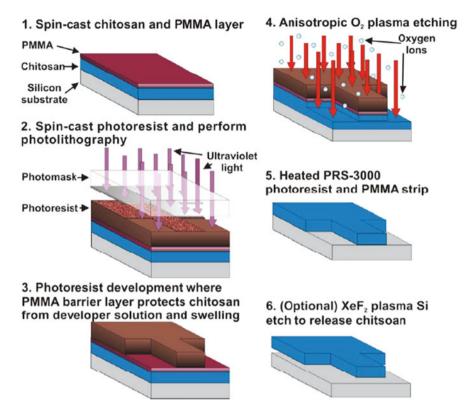

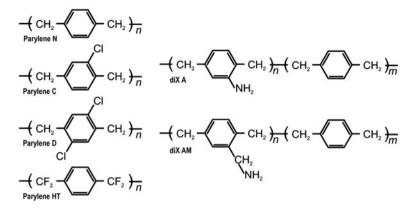

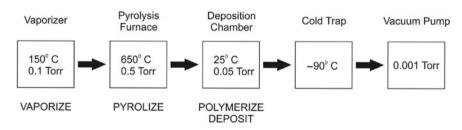

| 4.5 | Paryle |            |                                | 223        |

|     | 4.5.1  | Material P |                                | 224        |

|     | 4.5.2  |            | •                              | 225        |

|     | 4.5.3  |            |                                | 226        |

|     | 4.5.4  |            |                                | 226        |

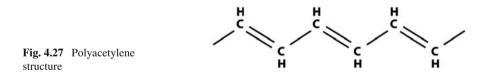

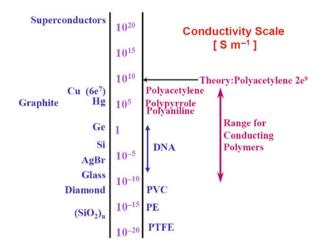

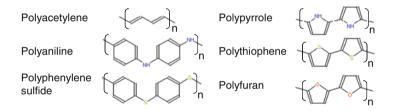

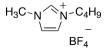

| 4.6 | Condu  |            |                                | 227        |

|     | 4.6.1  |            |                                | 228        |

|     | 4.6.2  |            | 1                              | 229        |

|     | 4.6.3  |            |                                | 230        |

|     |        | 4.6.3.1    |                                | 230        |

|     |        | 4.6.3.2    | Conducting Polymer as a Strain |            |

|     |        | 1101312    |                                | 231        |

|     | 4.6.4  | Processing | •                              | 231        |

|     | 1.0.1  | 4.6.4.1    |                                | 231        |

|     |        | 4.6.4.2    |                                | 232        |

|     |        | 4.6.4.3    | e                              | 232        |

|     |        | 4.6.4.4    |                                | 233        |

|     | 4.6.5  |            |                                | 233        |

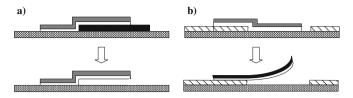

| 4.7 |        |            | 5                              | 235        |

| 1.7 | 4.7.1  | -          |                                | 235        |

|     | 4.7.2  | •          |                                | 238        |

| 4.8 |        |            |                                | 239<br>239 |

| 4.0 | 4.8.1  |            | •                              | 239        |

|     | 4.8.2  |            |                                | 235        |

|     | 4.0.2  | 4.8.2.1    |                                | 241        |

|     |        | 4.8.2.2    |                                | 242        |

|     |        | 4.8.2.2    | •                              | 242<br>242 |

|     |        | 4.8.2.3    |                                | 242<br>242 |

|     | 4.8.3  |            | · · · ·                        | 242<br>242 |

|     |        |            |                                |            |

|     | 4.8.4  |            |                                | 243        |

|     |        | 4.8.4.1    |                                | 243<br>244 |

|     |        | 4.8.4.2    |                                |            |

|     | 105    | 4.8.4.3    |                                | 245        |

|     | 4.8.5  |            | e                              | 246        |

|     |        | 4.8.5.1    | Milling                        | 246        |

|      |          | 4.8.5.2       | Laser                                    |

|------|----------|---------------|------------------------------------------|

|      |          | 4.8.5.3       | Focused Ion Beam                         |

|      |          | 4.8.5.4       | Fixture of Molds                         |

|      |          | 4.8.5.5       | Release Coatings                         |

|      | 4.8.6    | Process D     | evelopment                               |

|      | 4.8.7    | Minimum       | Substrate Thickness                      |

| 4.9  | Materi   | als Propertie | 8                                        |

| Refe | rences . |               |                                          |

| ۸ddi | tive Pro | cesses for I  | Piezoelectric Materials:                 |

|      |          |               | · · · · · · · · · · · · · · · · · · ·    |

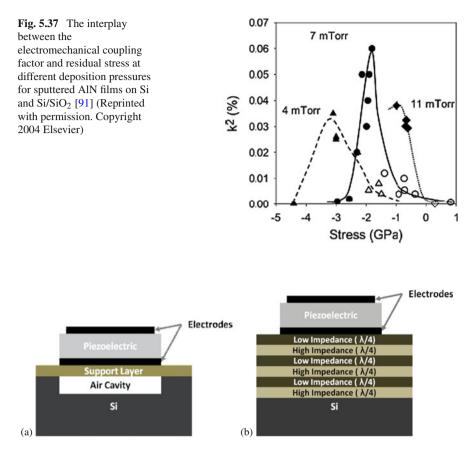

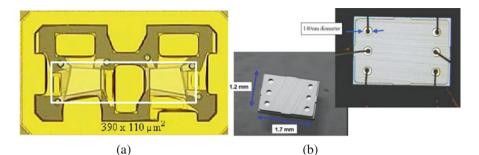

| 5.1  |          |               | zoelectric Thin Films                    |

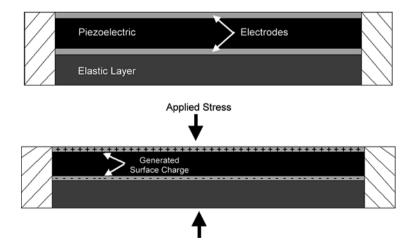

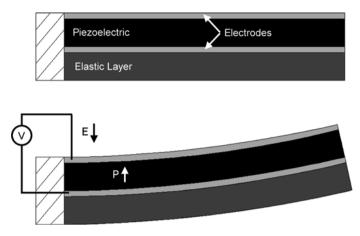

| 5.1  | 5.1.1    |               | Converse Piezoelectricity                |

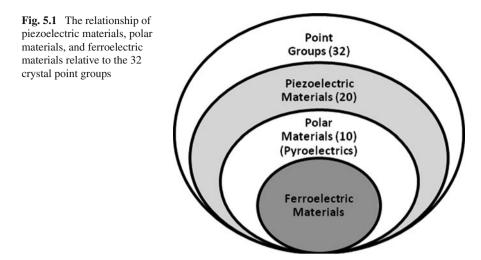

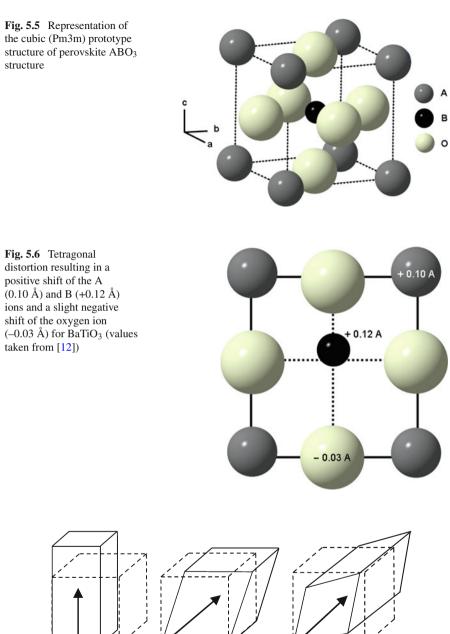

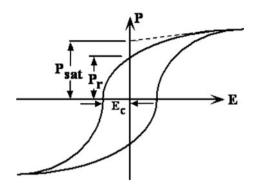

|      | 5.1.2    |               | – Ferroelectrics and Nonferroelectrics   |

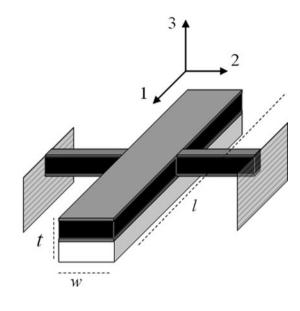

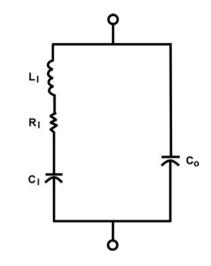

|      | 5.1.3    |               | tal Design Equations and Models          |

|      | UTTU     | 5.1.3.1       | Linear Constitutive Equations of         |

|      |          |               | Piezoelectricity                         |

|      |          | 5.1.3.2       | Electromechanical Coupling Factors       |

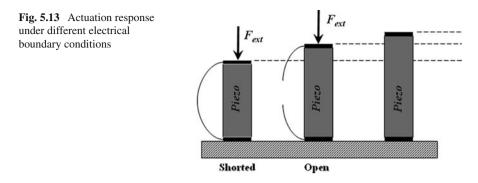

|      |          | 5.1.3.3       | Influence of Boundary Conditions         |

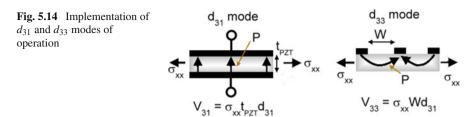

|      |          | 5.1.3.4       | Device Configurations                    |

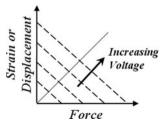

|      |          | 5.1.3.5       | Free Strain and Blocking Force           |

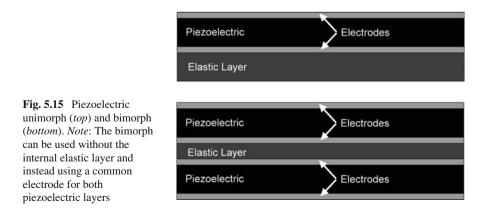

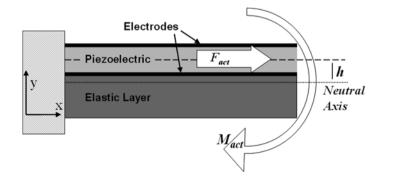

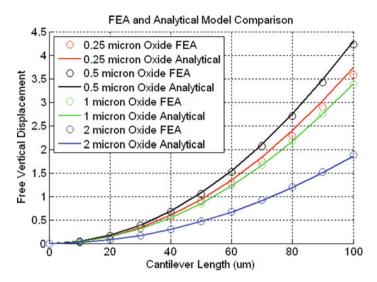

|      |          | 5.1.3.6       | Cantilever Unimorph Model                |

|      |          | 5.1.3.7       | Actuator Force Generation                |

|      |          |               | Against External Loads                   |

|      |          | 5.1.3.8       | Piezoelectric Sensing                    |

|      |          | 5.1.3.9       | Equivalent Circuit Models                |

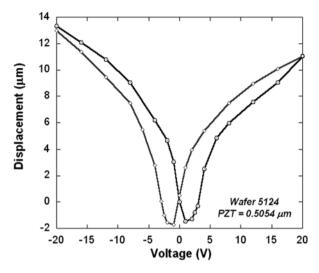

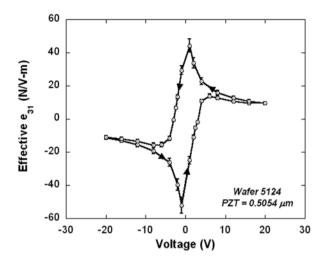

|      |          | 5.1.3.10      | Thin-Film Ferroelectric Nonlinearity     |

|      |          | 5.1.3.11      | Heat Generation                          |

|      | 5.1.4    | Materials     | Selection Guide                          |

|      | 5.1.5    | Applicatio    | ons                                      |

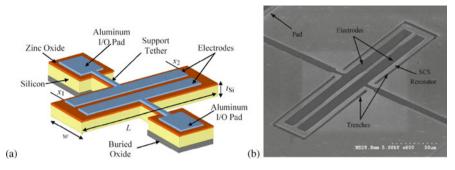

| 5.2  | Polar N  |               | N and ZnO                                |

|      | 5.2.1    | Material D    | Deposition                               |

|      | 5.2.2    | Patterning    | Techniques                               |

|      | 5.2.3    |               | esign Concerns                           |

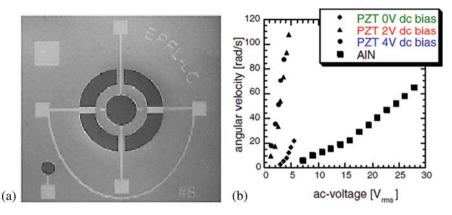

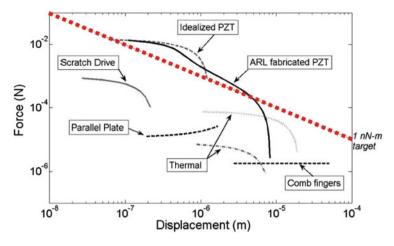

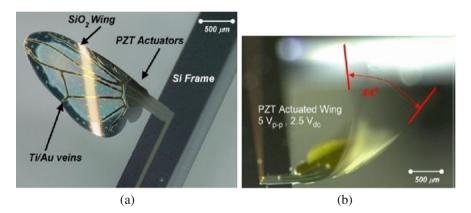

|      | 5.2.4    |               | amples                                   |

|      | 5.2.5    | Case Stud     | y                                        |

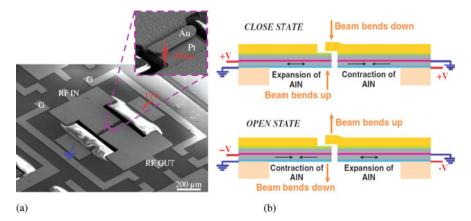

| 5.3  | Ferroe   | lectrics: PZT | ¬                                        |

|      | 5.3.1    | Material D    | Deposition                               |

|      | 5.3.2    |               | Techniques                               |

|      | 5.3.3    | -             | sign Concerns                            |

|      | 5.3.4    | Device Ex     | amples                                   |

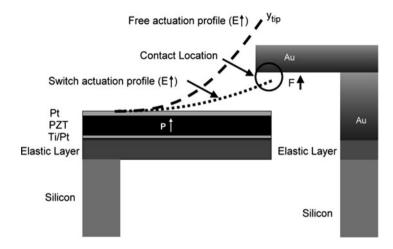

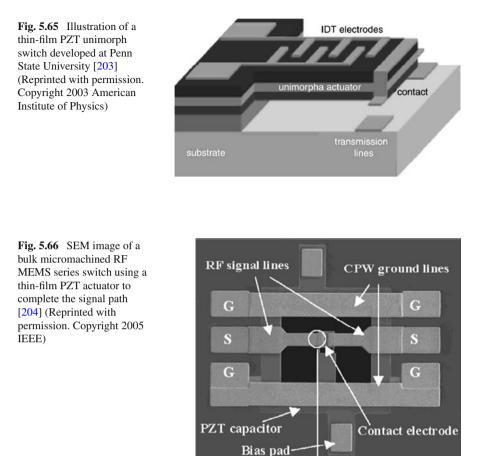

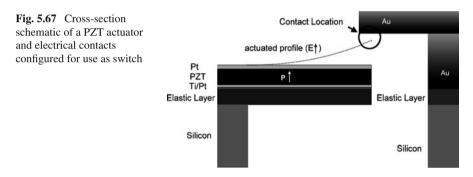

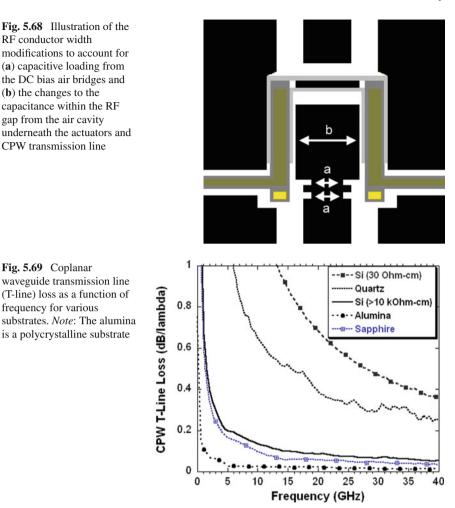

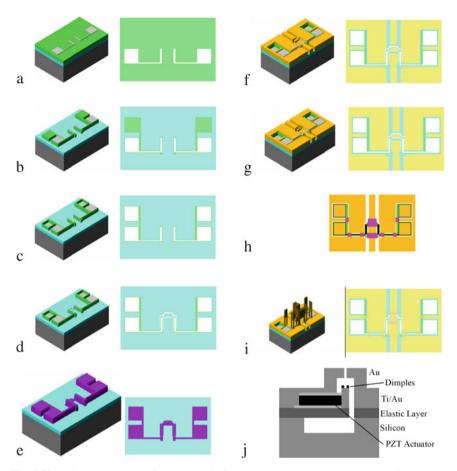

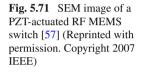

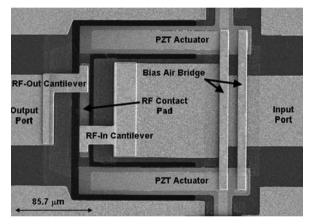

|      | 5.3.5    | Case Stud     | y on the Design and Processing of a      |

|      |          | RF MEMS       | S Switch Using PZT Thin-Film Actuators . |

| 6 | Mate             | erials an                              | d Processes in Shape Memory Alloy                                                    |

|---|------------------|----------------------------------------|--------------------------------------------------------------------------------------|

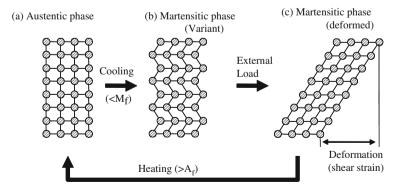

|   | 6.1              | Introdu                                | action and Principle                                                                 |

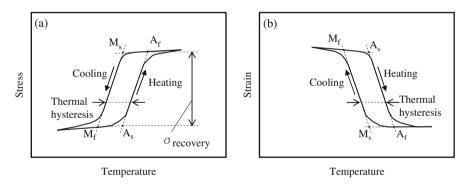

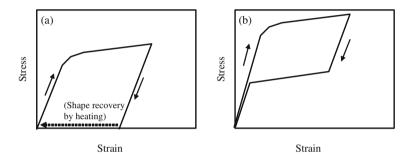

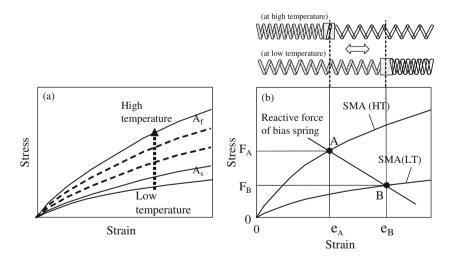

|   |                  | 6.1.1                                  | Basic Principle                                                                      |

|   |                  | 6.1.2                                  | Introduction of TiNi and TiNi-Base Ternary Alloys 357                                |

|   |                  | 6.1.3                                  | Super-Elasticity                                                                     |

|   |                  | 6.1.4                                  | One-Way Type, Two-Way Type,                                                          |

|   |                  |                                        | All-Round-Way Type                                                                   |

|   | 6.2              | als Properties and Fabrication Process |                                                                                      |

|   |                  |                                        | A Actuators                                                                          |

|   |                  | 6.2.1                                  | Bulk Material                                                                        |

|   |                  | 6.2.2                                  | Thin Film                                                                            |

|   |                  |                                        | 6.2.2.1 Sputtering                                                                   |

|   |                  |                                        | 6.2.2.2 Evaporation                                                                  |

|   |                  |                                        | 6.2.2.3 Non-planar Thin Film Deposition 363                                          |

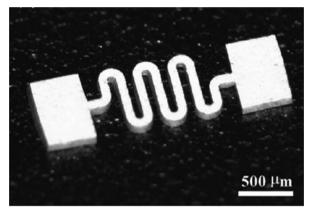

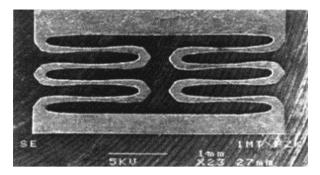

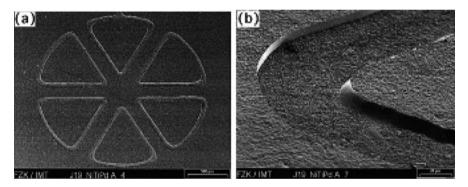

|   |                  | 6.2.3                                  | Micromachining                                                                       |

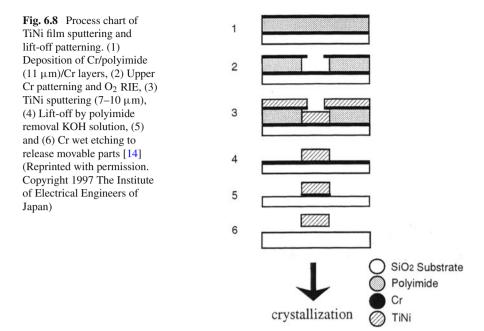

|   |                  | 6.2.4                                  | Etching and Lift-Off                                                                 |

|   |                  | 0.2.4                                  | 6.2.4.1 Case and Example                                                             |

|   |                  | 6.2.5                                  | Assembly                                                                             |

|   |                  | 0.2.5                                  | 6.2.5.1 Mechanical Fixation                                                          |

|   |                  |                                        | 6.2.5.2 Adhesion                                                                     |

|   |                  |                                        | 6.2.5.3 Welding                                                                      |

|   |                  |                                        |                                                                                      |

|   |                  | 6.2.6                                  | 6.2.5.4 Soldering                                                                    |

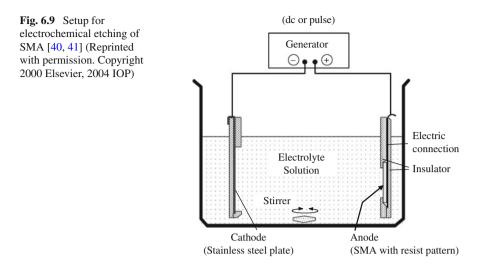

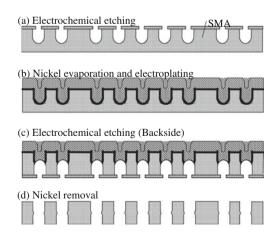

|   |                  | 0.2.0                                  |                                                                                      |

|   |                  |                                        |                                                                                      |

|   | 62               | A                                      | 6.2.6.2 Process                                                                      |

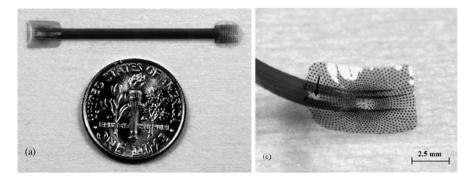

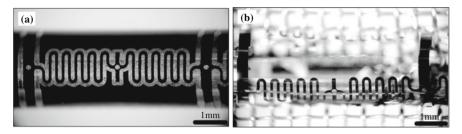

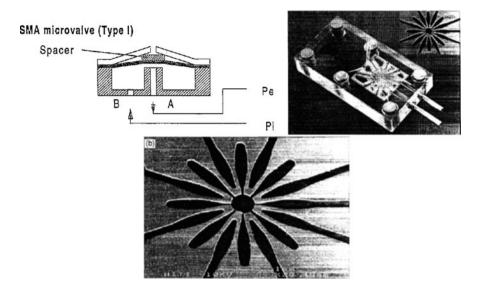

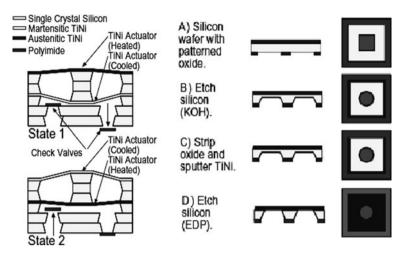

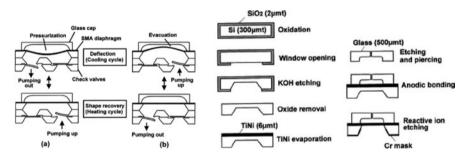

|   | 6.3              |                                        | ations and Devices                                                                   |

|   |                  | 6.3.1                                  | Medical                                                                              |

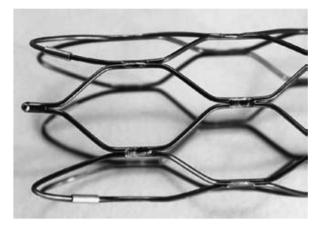

|   |                  |                                        | 6.3.1.1 Stents                                                                       |

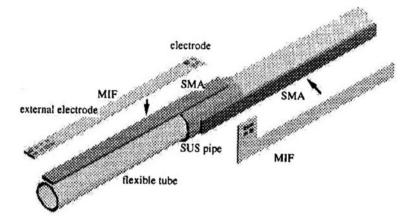

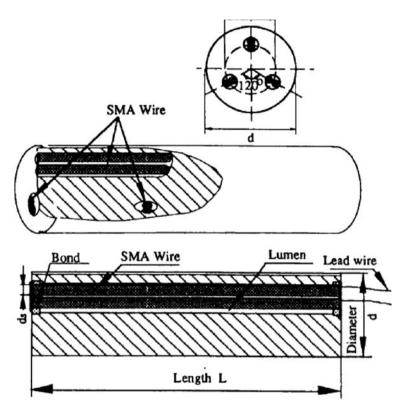

|   |                  |                                        | 6.3.1.2 Endoscopes                                                                   |

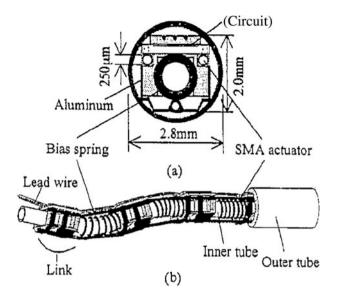

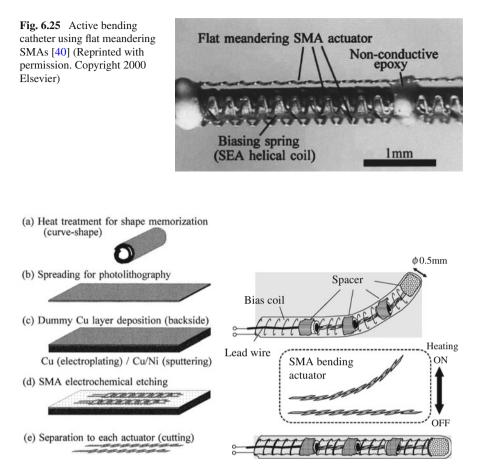

|   |                  |                                        | 6.3.1.3 Catheters 379                                                                |

|   |                  | ( ) )                                  | 6.3.1.4 Micro Clips and Grippers                                                     |

|   |                  | 6.3.2                                  | Fluidic Devices                                                                      |

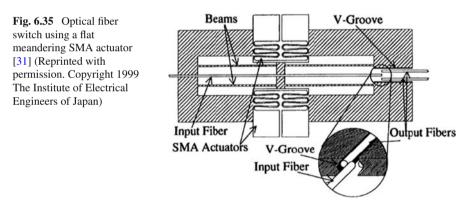

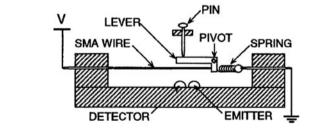

|   |                  | 6.3.3                                  | Optical Fiber Switch                                                                 |

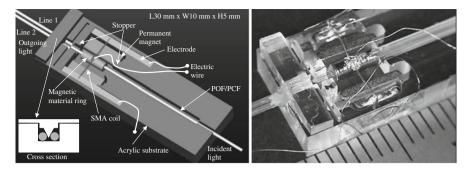

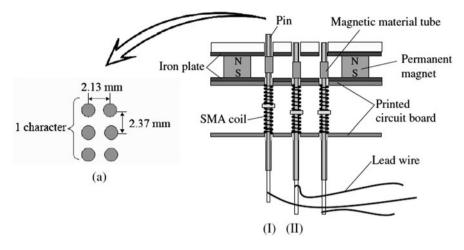

|   |                  | 6.3.4                                  | Tactile Pin Display   390                                                            |

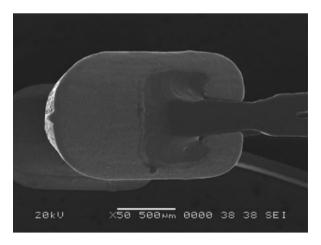

|   |                  | 6.3.5                                  | AFM Cantilever                                                                       |

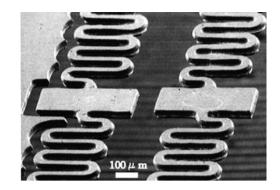

|   |                  | 6.3.6                                  | Case Studies and Lessons Learned                                                     |

|   |                  |                                        | 6.3.6.1 Designs                                                                      |

|   |                  |                                        | 6.3.6.2 Heating and Cooling                                                          |

|   | 6.4              |                                        | ary                                                                                  |

|   | Refer            | rences .                               |                                                                                      |

| 7 | Drv <sup>1</sup> | Etching                                | for Micromachining Applications                                                      |

| • | 7.1              |                                        | ching $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $40^4$ |

|   |                  | 7.1.1                                  | Etch Metrics                                                                         |

|   | 7.2              |                                        | a Etching                                                                            |

|   |                  | i mont                                 |                                                                                      |

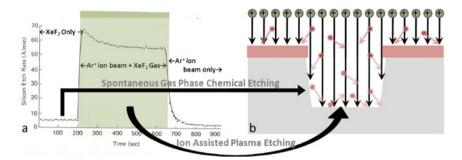

|   |      | 7.2.1    | Types of Etching                                                                                         | 408 |

|---|------|----------|----------------------------------------------------------------------------------------------------------|-----|

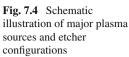

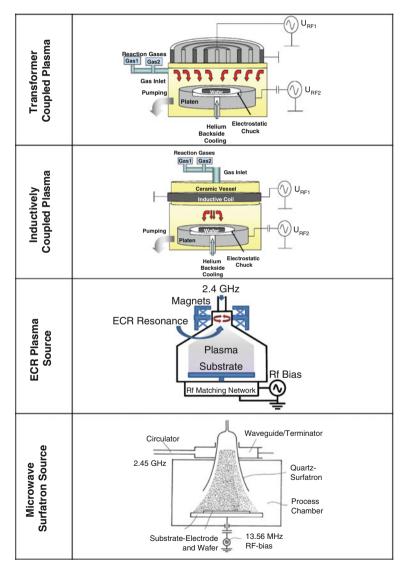

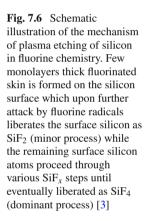

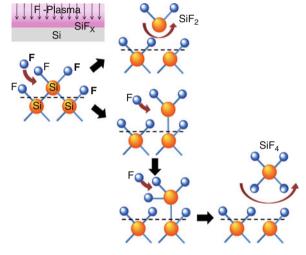

|   |      | 7.2.2    | Plasma Sources                                                                                           | 412 |

|   | 7.3  | Plasma   | a Process Parameters and Control                                                                         | 418 |

|   |      | 7.3.1    | Energy-Driven Anisotropy                                                                                 | 419 |

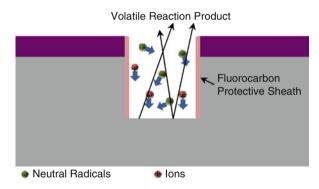

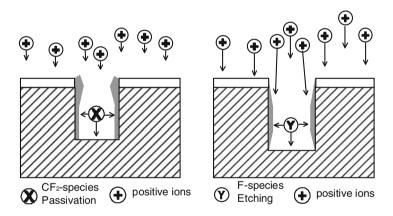

|   |      | 7.3.2    | Inhibitor-Driven Anisotropy                                                                              | 420 |

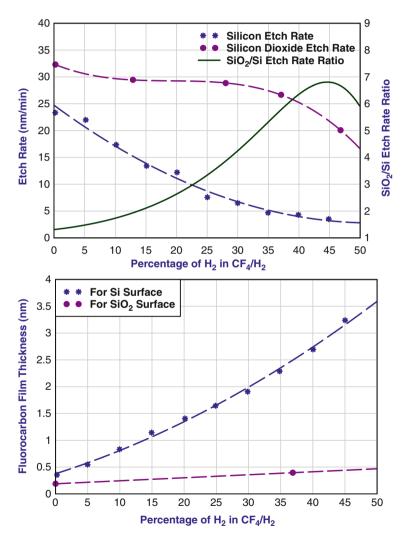

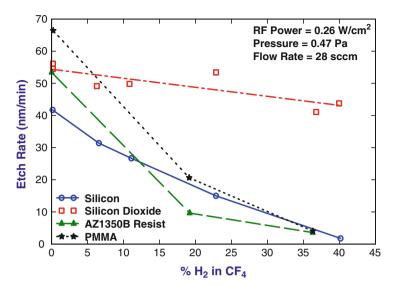

|   |      | 7.3.3    | Selectivity in Plasma Etching                                                                            | 421 |

|   | 7.4  | Case S   | Study: Etching Silicon, Silicon Dioxide,                                                                 |     |

|   |      |          | licon Nitride                                                                                            | 422 |

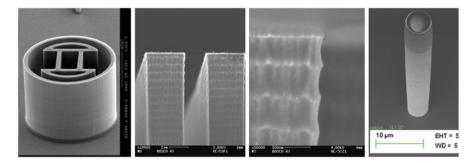

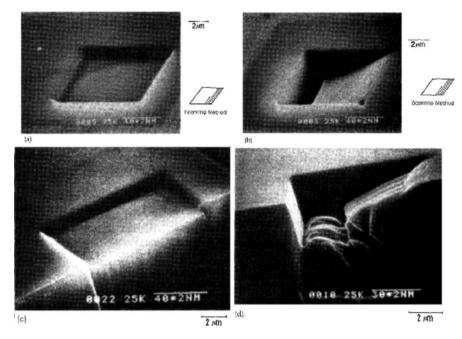

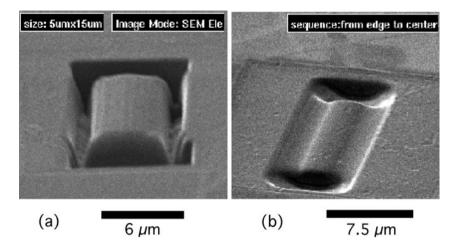

|   | 7.5  |          | Study: High-Aspect-Ratio Silicon Etch Process                                                            | 427 |

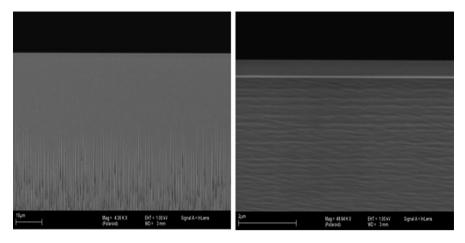

|   |      | 7.5.1    | Cryogenic Dry Etching                                                                                    | 428 |

|   |      | 7.5.2    | Bosch Process                                                                                            | 429 |

|   |      | 7.5.3    | Understanding Trends for DRIE Recipe                                                                     |     |

|   |      |          | Development                                                                                              | 432 |

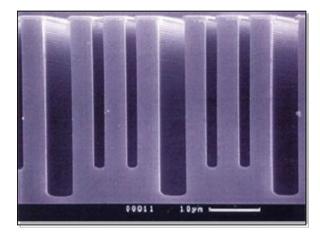

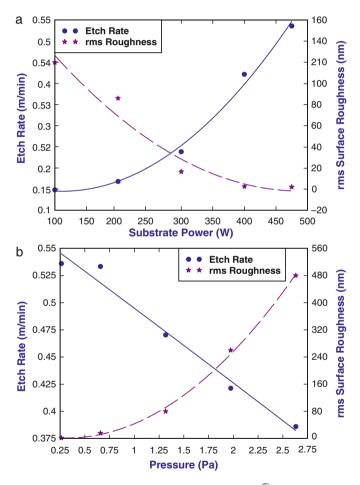

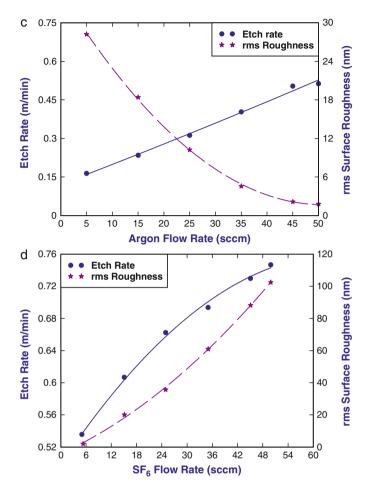

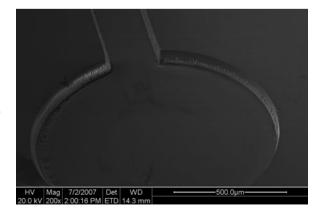

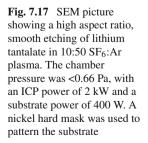

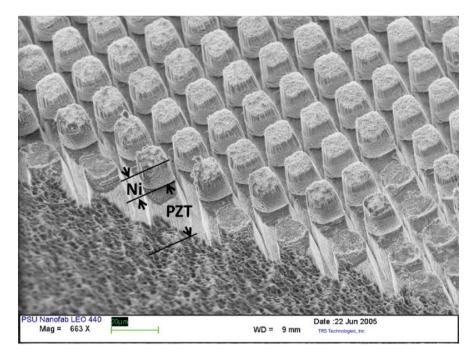

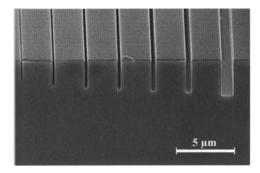

|   | 7.6  | High-A   | Aspect-Ratio Etching of Piezoelectric Materials                                                          | 434 |

|   |      | 7.6.1    | Case Study: High-Aspect-Ratio Etching of                                                                 |     |

|   |      |          | Glass (Pyrex <sup><math>\mathbb{R}</math></sup> ) and Quartz $\ldots \ldots \ldots \ldots \ldots \ldots$ | 434 |

|   |      | 7.6.2    | High-Aspect-Ratio Etching of Piezoelectric                                                               |     |

|   |      |          | Materials                                                                                                | 438 |

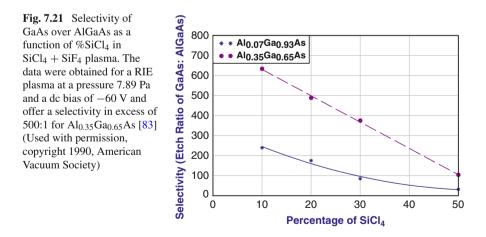

|   | 7.7  | Etchin   | g of Compound Semiconductors                                                                             | 441 |

|   |      | 7.7.1    | Case Study: Etching of GaAs and AlGaAs                                                                   | 441 |

|   |      | 7.7.2    | Case Study: Etching of InP, InGaAs, InSb,                                                                |     |

|   |      |          | and InAs                                                                                                 | 444 |

|   | 7.8  |          | Study: Ion Beam Etching                                                                                  | 446 |

|   | 7.9  | Summ     | ary                                                                                                      | 449 |

|   | Refe | rences . |                                                                                                          | 452 |

| 8 | MEN  | AS Wet-  | Etch Processes and Procedures                                                                            | 457 |

|   | 8.1  |          | uction                                                                                                   | 458 |

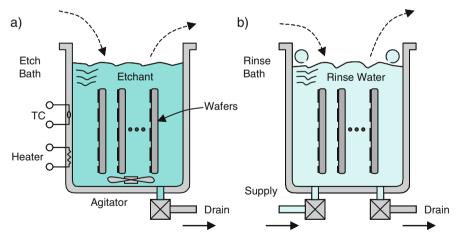

|   | 8.2  |          | bles and Process Architectures for Wet Etching                                                           | 460 |

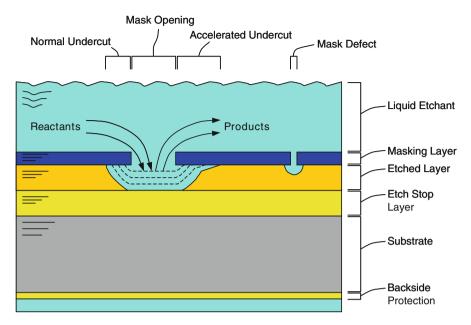

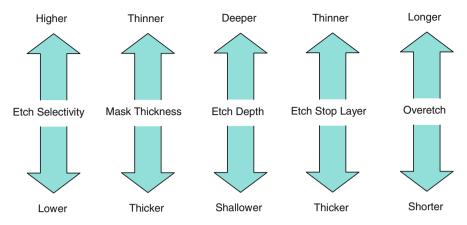

|   |      | 8.2.1    | Surface Reactions and Reactant/Product Transport                                                         | 464 |

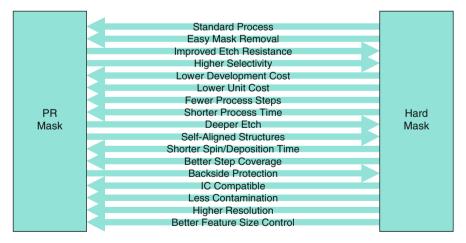

|   |      | 8.2.2    | Etchant Selectivity and Masking Considerations                                                           | 467 |

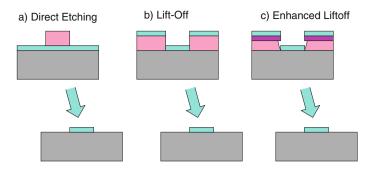

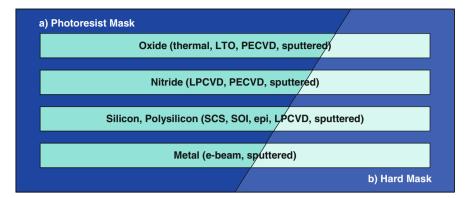

|   |      | 8.2.3    | Direct Etching and Liftoff Techniques                                                                    | 469 |

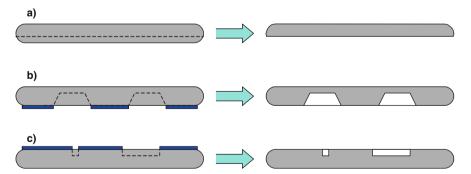

|   |      | 8.2.4    | Sacrificial Layer Removal                                                                                | 470 |

|   |      | 8.2.5    | Substrate Thinning and Removal                                                                           | 471 |

|   |      | 8.2.6    | Impact on Process Architecture                                                                           | 472 |

|   |      | 8.2.7    | Process Development for Wet Etches                                                                       | 473 |

|   |      | 8.2.8    | Additional Considerations and Alternatives                                                               | 476 |

|   | 8.3  | Evalua   | tion and Development of Wet-Etch Facilities                                                              |     |

|   |      | and Pr   | ocedures                                                                                                 | 479 |

|   |      | 8.3.1    | Facility Requirements                                                                                    | 479 |

|   |      |          | 8.3.1.1 General Facilities                                                                               | 479 |

|   |      |          | 8.3.1.2 Wet-Bench Services                                                                               | 480 |

|   |      |          | 8.3.1.3 Wet-Bench Equipment                                                                              | 480 |

|   |      |          | 8.3.1.4 Safety                                                                                           | 481 |

|   |      | 8.3.2    | Wafer Handling Considerations                                                                            | 482 |

|     | 8.3.3  | Safety Concerns                                 | 483 |

|-----|--------|-------------------------------------------------|-----|

|     | 8.3.4  | Training                                        | 483 |

| 8.4 | IC-Co  | mpatible Materials and Wet Etching              | 484 |

|     | 8.4.1  | Oxide and Dielectric Etching                    | 484 |

|     | 8.4.2  | Silicon, Polysilicon, and Germanium Isotropic   |     |

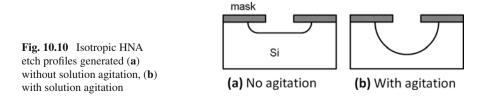

|     |        | Etching                                         | 492 |

|     | 8.4.3  | Standard Metal Etching                          | 495 |

|     | 8.4.4  | Photoresist Removal Techniques and Wafer        |     |

|     |        | Cleaning Processes                              | 501 |

|     | 8.4.5  | Examples: Wet Chemical Etching of               |     |

|     |        | IC-Compatible Materials                         | 513 |

|     |        | 8.4.5.1 Example 1: Wet Etch of                  |     |

|     |        | Low-Temperature Oxide                           | 514 |

|     |        | 8.4.5.2 Example 2: Wet Etch of Silicon          | 011 |

|     |        | Nitride on Silicon                              | 515 |

|     |        | 8.4.5.3 Example 3: Sacrificial Etch of          | 010 |

|     |        | Deposited Polysilicon Under                     |     |

|     |        | a Structural Layer of                           |     |

|     |        | Stress-Controlled Silicon Nitride               | 515 |

|     |        | 8.4.5.4 Example 4: Aluminum Etching             |     |

|     |        | over Patterned Nitride, Oxide,                  |     |

|     |        | and Silicon                                     | 515 |

|     |        | 8.4.5.5 Example 5: Junction Depth               |     |

|     |        | Determination for an Integrated                 |     |

|     |        | MEMS Device                                     | 515 |

| 8.5 | Nonsta | andard Materials and Wet Etching                | 516 |

|     | 8.5.1  | Nonstandard Dielectric, Semiconductor, and      |     |

|     |        | Metal Etching                                   | 517 |

|     | 8.5.2  | Plastic and Polymer Etching                     | 517 |

|     | 8.5.3  | Examples: Wet Chemical Etching of               |     |

|     |        | Nonstandard Materials                           | 570 |

|     |        | 8.5.3.1 Example 1: BCB Patterning and Etching . | 570 |

|     |        | 8.5.3.2 Example 2: COC Patterning and           |     |

|     |        | Solvent Bonding                                 | 579 |

|     |        | 8.5.3.3 Example 3: LIGA Mold Removal            | 579 |

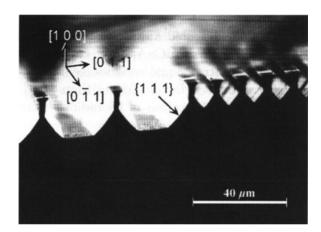

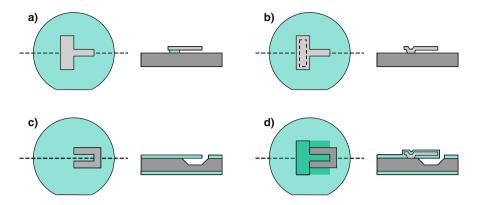

| 8.6 | Anisot | tropic Silicon Etching and Silicon Etch Stops   | 579 |

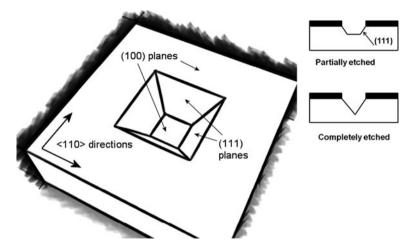

|     | 8.6.1  | Anisotropic Etching of Silicon                  | 581 |

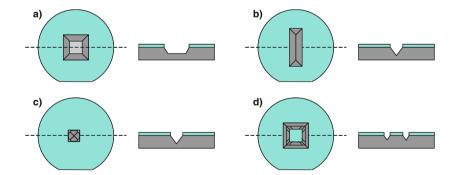

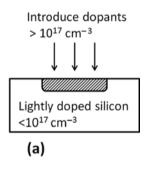

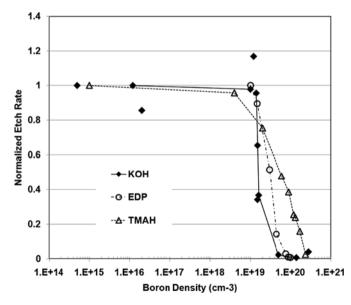

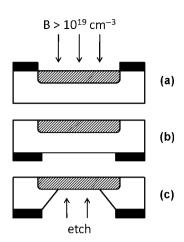

|     | 8.6.2  | Heavily Doped Silicon Etch Stops                | 582 |

|     | 8.6.3  | Lightly Doped Silicon and Silicon–Germanium     |     |

|     |        | Etch Stops                                      | 589 |

|     | 8.6.4  | Ion-Implanted Silicon Etch Stops                | 589 |

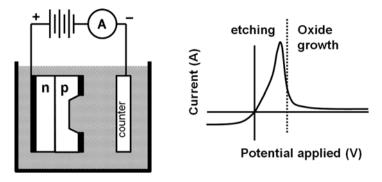

|     | 8.6.5  | Electrochemical Etching and Electrochemical     |     |

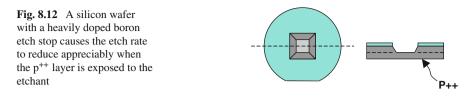

|     |        | Etch Stops                                      | 595 |

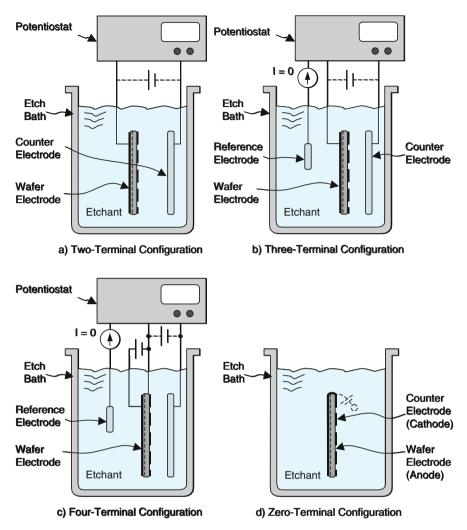

|     | 8.6.6  | Photoassisted Silicon Etching and Etch Stops    | 597 |

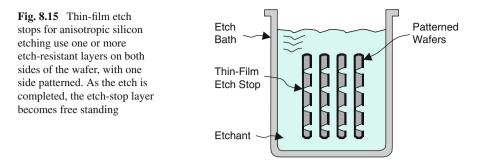

|     | 8.6.7  | Thin-Film Etch Stops                            | 601 |

|     | 8.6.8          | Examples     | s: Wet Chemical and Electrochemical    |      |

|-----|----------------|--------------|----------------------------------------|------|

|     |                | Etch Stop    | 08                                     | 603  |

|     |                | 8.6.8.1      | Example 1: Anisotropic Silicon         |      |

|     |                |              | Etching of an SOI Wafer                | 603  |

|     |                | 8.6.8.2      | Example 2: Heavy Boron-Doped           |      |

|     |                |              | Etch Stop                              | 604  |

|     |                | 8.6.8.3      | Example 3: Electrochemical Etch Stop   | 604  |

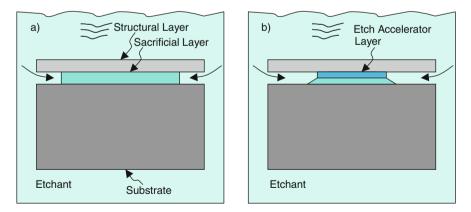

| 8.7 | Sacrifi        | cial Laver H | Etching                                | 608  |

|     | 8.7.1          |              | l Layer Removal Techniques             | 610  |

|     | 8.7.2          |              | l Oxide Removal for Polysilicon        | 010  |

|     | 01112          |              |                                        | 611  |

|     | 8.7.3          |              | ve Sacrificial and Structural Layer    | 011  |

|     | 0.7.5          |              | tions                                  | 611  |

|     | 8.7.4          |              | elerator Layers for Enhanced           | 011  |

|     | 0.7.4          |              | l Layer Removal                        | 617  |

|     | 8.7.5          |              | quid Removal and Antistiction Coatings | 619  |

|     | 8.7.5<br>8.7.6 |              | s: Sacrificial Layer Removal and       | 019  |

|     | 0.7.0          |              |                                        | 620  |

|     |                | 8.7.6.1      | Layer Release                          | 020  |

|     |                | 8.7.0.1      |                                        |      |

|     |                |              | Controlled Polysilicon with an         | 620  |

|     |                | 07()         | Oxide Sacrificial Layer                | 620  |

|     |                | 8.7.6.2      | Example 2: Poly-SiGe on a              | (20) |

|     |                | 0 7 6 0      | Patterned Oxide/Nitride Laminate       | 620  |

|     |                | 8.7.6.3      | Example 3: Silicon Nitride on a        | (22) |

|     |                |              | Polysilicon Sacrificial Layer          | 623  |

|     | _              | 8.7.6.4      | Example 4: Aluminum on Photoresist     | 623  |

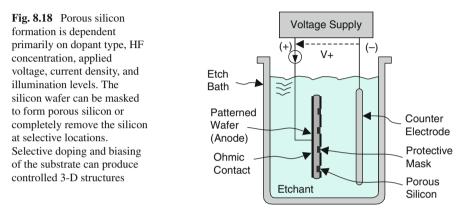

| 8.8 |                |              | rmation with Wet Chemistry             | 623  |

|     | 8.8.1          |              | ous, Mesoporous, and Macroporous       |      |

|     |                |              | ormation                               | 624  |

|     | 8.8.2          |              | Porous Silicon Removal                 | 625  |

|     | 8.8.3          |              | s: Porous Silicon Formation            | 625  |

|     |                | 8.8.3.1      | Example 1: Chemical Porous             |      |

|     |                |              | Silicon Formation                      | 625  |

|     |                | 8.8.3.2      | Example 2: Nanoporous Silicon          |      |

|     |                |              | Formation                              | 628  |

|     |                | 8.8.3.3      | Example 3: Mesoporous Silicon          |      |

|     |                |              | Formation                              | 628  |

|     |                | 8.8.3.4      | Example 4: Macroporous Silicon         |      |

|     |                |              | Formation                              | 629  |

| 8.9 | Layer          | Delineation  | and Defect Determination               |      |

|     |                |              | 3                                      | 629  |

|     | 8.9.1          |              | evel and Defect Determination with     |      |

|     |                | 1            | ants                                   | 630  |

|     | 8.9.2          |              | lineation with Wet Etchants            | 636  |

|     |                |              |                                        |      |

|   |       | 8.9.3           | Examples    | : Layer Delineation and Defect           |     |

|---|-------|-----------------|-------------|------------------------------------------|-----|

|   |       |                 | Determin    | ation                                    | 637 |

|   |       |                 | 8.9.3.1     | Example 1: Metallurgical Junction        |     |

|   |       |                 |             | Determination                            | 637 |

|   |       |                 | 8.9.3.2     | Example 2: Cross-Sectioning and          |     |

|   |       |                 |             | Layer Delineation                        | 637 |

|   | Refer | ences .         |             |                                          | 638 |

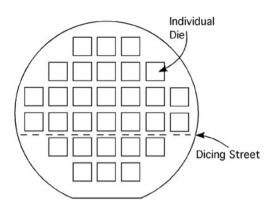

| 9 | MEN   | <b>AS</b> Litho | ography an  | d Micromachining Techniques              | 667 |

|   | 9.1   | Overvi          |             | · · · · · · · · · · · · · · · · · · ·    | 667 |

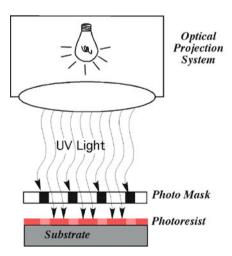

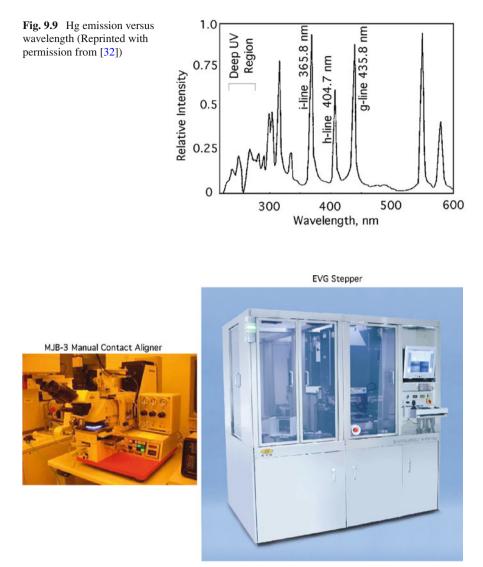

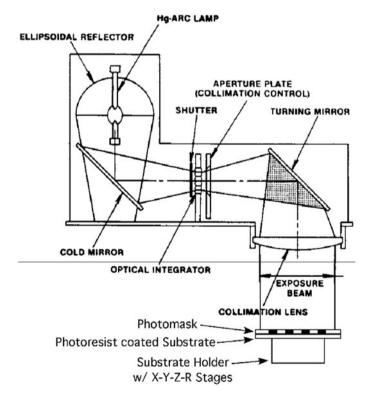

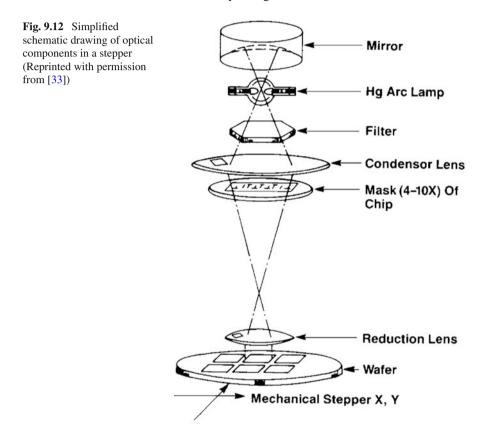

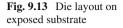

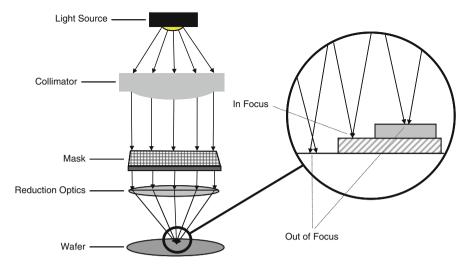

|   | 9.2   | UV Lit          |             |                                          | 672 |

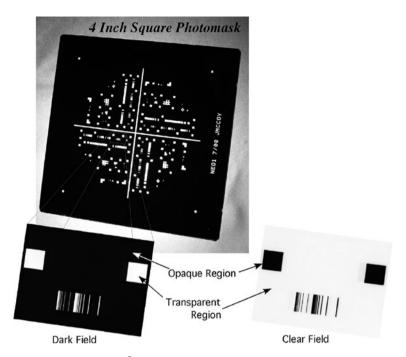

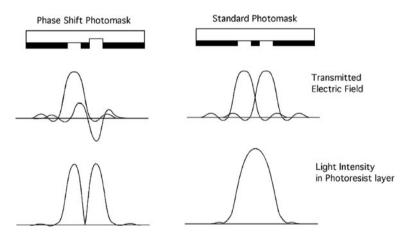

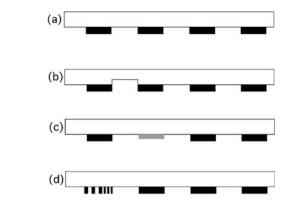

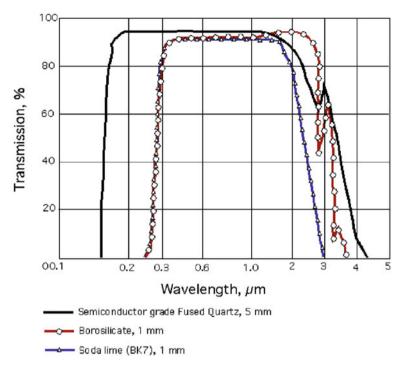

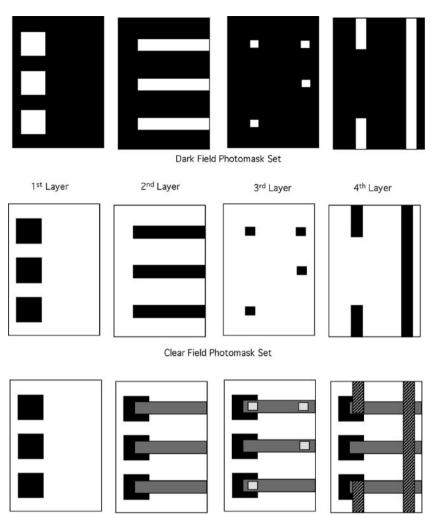

|   |       | 9.2.1           |             | usks                                     | 672 |

|   |       | 9.2.2           |             | rojection Systems                        | 677 |

|   |       |                 | 9.2.2.1     | Contact Aligner                          | 677 |

|   |       |                 | 9.2.2.2     | Stepper                                  | 681 |

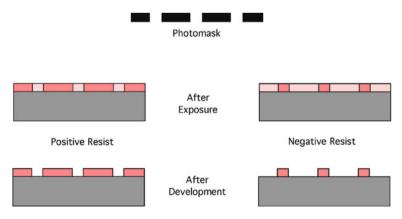

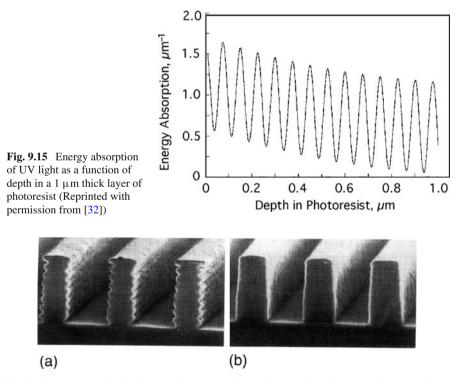

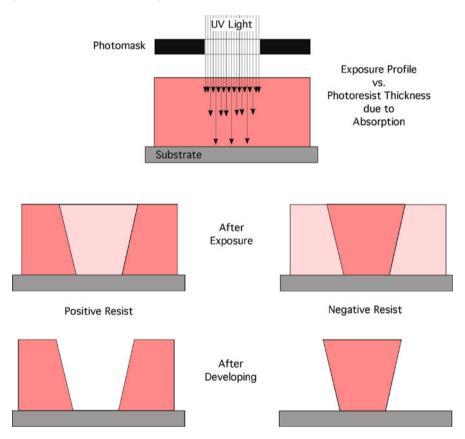

|   |       | 9.2.3           | Photoresi   | st                                       | 682 |

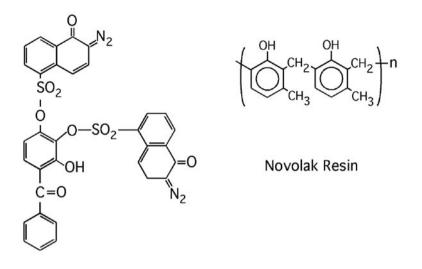

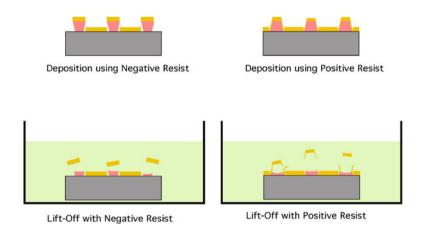

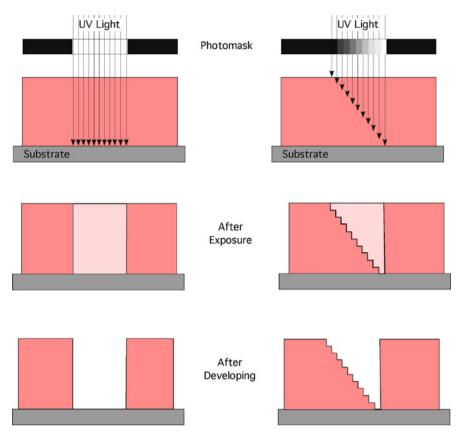

|   |       |                 | 9.2.3.1     | Positive Photoresist                     | 684 |

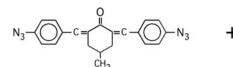

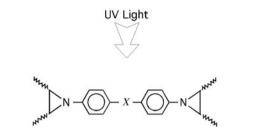

|   |       |                 | 9.2.3.2     | Negative Photoresist                     | 686 |

|   |       |                 | 9.2.3.3     | Image Reversal for Positive              |     |

|   |       |                 |             | Resist (Converting Positive Resist       |     |

|   |       |                 |             | into a Negative Resist)                  | 687 |

|   |       | 9.2.4           | Substrate   |                                          | 688 |

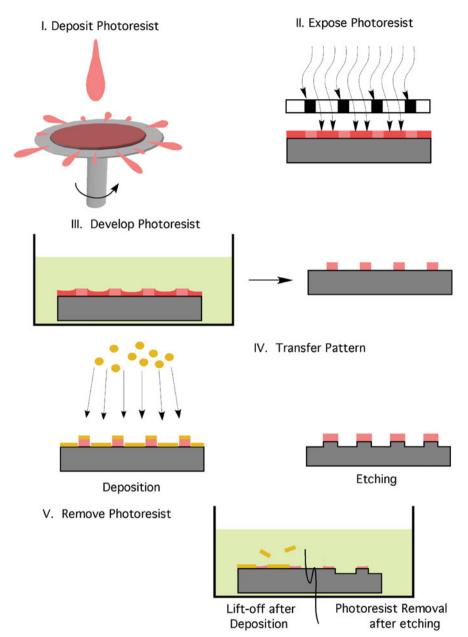

|   |       | 9.2.5           | Processin   | g Steps for UV Lithography               | 688 |

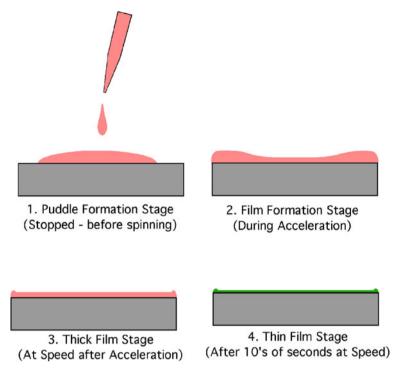

|   |       |                 | 9.2.5.1     | Deposit Photoresist                      | 688 |

|   |       |                 | 9.2.5.2     | Expose Photoresist                       | 690 |

|   |       |                 | 9.2.5.3     | Develop Photoresist                      | 691 |

|   |       |                 | 9.2.5.4     | Transfer Pattern                         | 691 |

|   |       |                 | 9.2.5.5     | Remove Photoresist                       | 692 |

|   | 9.3   |                 | ale Lithogr |                                          | 693 |

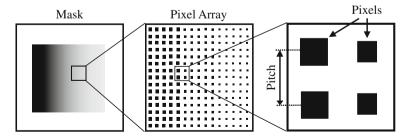

|   |       | 9.3.1           |             | sk Pixelation                            | 696 |

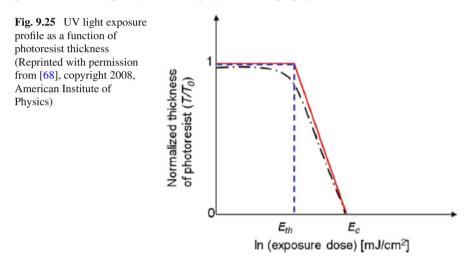

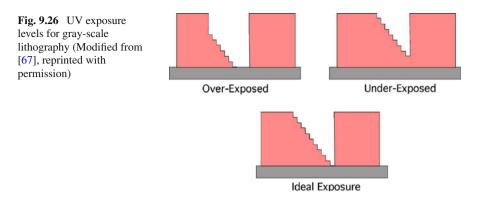

|   |       | 9.3.2           | Photoresi   | st Properties for Grayscale Lithography  | 697 |

|   |       |                 | 9.3.2.1     | Contrast and Thickness                   | 697 |

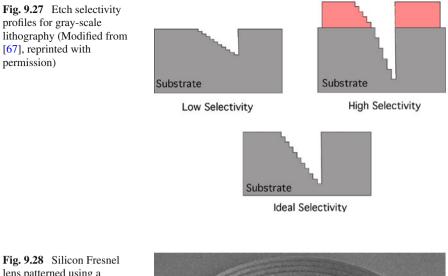

|   |       |                 | 9.3.2.2     | Exposure and Developing Times            | 697 |

|   |       |                 | 9.3.2.3     | Etch Selectivity                         | 698 |

|   | 9.4   | •               |             | у                                        | 698 |

|   |       | 9.4.1           | X-Ray M     |                                          | 700 |

|   |       | 9.4.2           | •           | notoresists                              | 702 |

|   |       | 9.4.3           | -           |                                          | 702 |

|   |       | 9.4.4           |             | nent                                     | 703 |

|   | 9.5   |                 |             | ography                                  | 704 |

|   |       | 9.5.1           |             | Lithography                              | 704 |

|   |       | 9.5.2           |             | Lithography and Focused Ion Beam (FIB) . | 708 |

|   |       | 9.5.3           |             | sted Electron and Ion Beam Lithography   | 710 |

|   |       | 9.5.4           | Dip-Pen l   | Lithography (DPN)                        | 711 |

|     | 9.5.5    | Direct-Write Laser                                              | 712 |

|-----|----------|-----------------------------------------------------------------|-----|

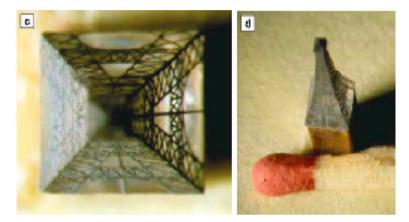

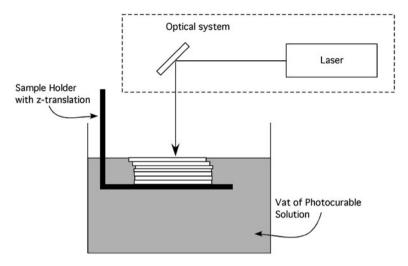

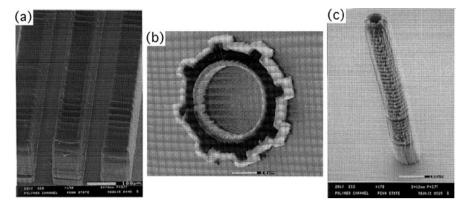

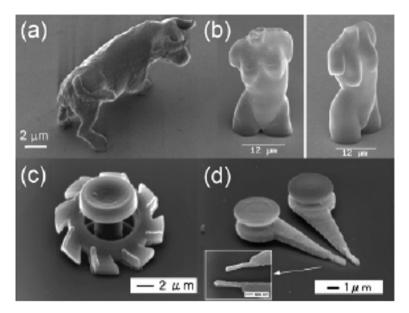

|     | 9.5.6    | Stereolithography and Microstereolithography                    | 714 |

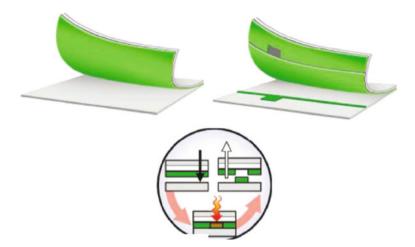

| 9.6 | Print/Ir | nprint Lithography                                              | 716 |

|     | 9.6.1    | Inkjet Printing                                                 | 719 |

|     | 9.6.2    | Soft Lithography                                                | 720 |

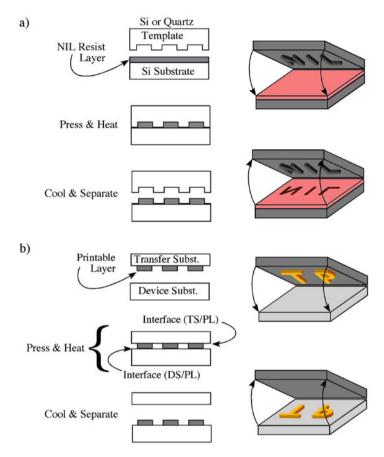

|     | 9.6.3    | Nanoimprint Lithography (NIL)                                   | 720 |

|     | 9.6.4    | Transfer Printing                                               | 722 |

| 9.7 | Case St  | tudies                                                          | 725 |

|     | 9.7.1    | Case Study 1: Substrate Cleaning-RCA Clean(s)                   | 725 |

|     |          | 9.7.1.1 Recipe Steps                                            | 726 |

|     |          | 9.7.1.2 Notes                                                   | 727 |

|     | 9.7.2    | Case Study 2: Substrate Cleaning, O <sub>2</sub> Plasma Clean . | 727 |

|     |          | 9.7.2.1 Recipe Steps                                            | 727 |

|     |          | 9.7.2.2 Note                                                    | 727 |

|     | 9.7.3    | Case Study 3: Substrate Cleaning, Solvent Clean                 | 728 |

|     |          | 9.7.3.1 Recipe Steps                                            | 728 |

|     |          | 9.7.3.2 Note                                                    | 728 |

|     | 9.7.4    | Case Study 4: Positive Photoresist Processing:                  |     |

|     |          | General Processing for Shipley 1800 Series                      |     |

|     |          | Photoresist                                                     | 728 |

|     |          | 9.7.4.1 Recipe Steps                                            | 728 |

|     | 9.7.5    | Case Study 5: Positive Photoresist Processing:                  |     |

|     |          | Specific Processing for Shipley S1813                           | 729 |

|     |          | 9.7.5.1 Recipe Steps                                            | 729 |

|     | 9.7.6    | Case Study 6: Positive Photoresist Processing:                  |     |

|     |          | Specific Processing for OiR 906-10                              | 730 |

|     |          | 9.7.6.1 Recipe Steps                                            | 730 |

|     |          | 9.7.6.2 Notes                                                   | 731 |

|     | 9.7.7    | Case Study 7: Negative Photoresist                              |     |

|     |          | Processing: Specific Processing for NR7-1500PY                  | 731 |

|     |          | 9.7.7.1 Recipe Steps                                            | 731 |

|     |          | 9.7.7.2 Note 1                                                  | 732 |

|     |          | 9.7.7.3 Note 2                                                  | 733 |

|     | 9.7.8    | Case Study 8: E-Beam Lithography                                | 733 |

|     |          | 9.7.8.1 Notes on Using the NPGS Software                        | 735 |

|     | 9.7.9    | Case Study 9: Fabrication of PDMS Templates                     | 735 |

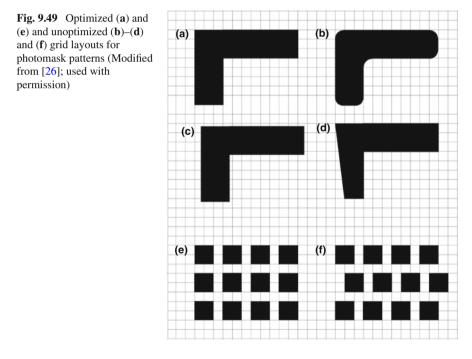

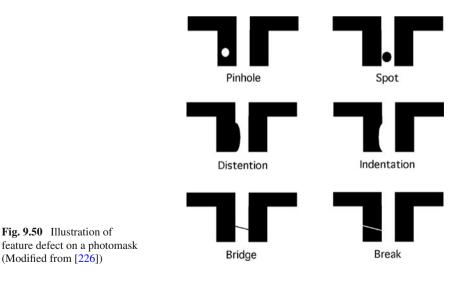

|     | 9.7.10   | Case Study 10: Photomask Fabrication [226, 227]                 | 736 |

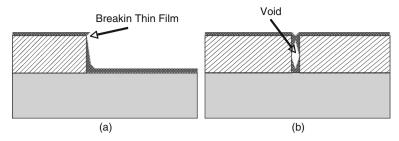

|     |          | 9.7.10.1 Photomask Defects                                      | 738 |

|     |          | 9.7.10.2 Grayscale Lithography Pixelated                        |     |

|     |          | Photomasks                                                      | 739 |

|     |          | 9.7.10.3 Mask Manufacturers                                     | 740 |

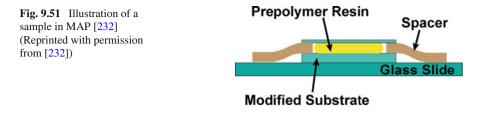

|     | 9.7.11   | Case Study 11: Multiphoton Absorption                           |     |

|     |          | Polymerization (MAP)                                            | 740 |

|     |          |                                                                 |     |

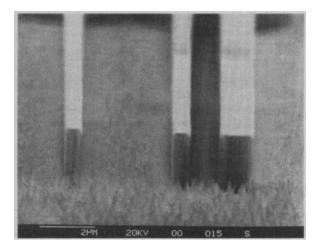

|    |                     | 9.7.12   | Case Study 12: Lithography Using Focused<br>Ion Beams |

|----|---------------------|----------|-------------------------------------------------------|

|    | Refer               | ences .  | 743                                                   |

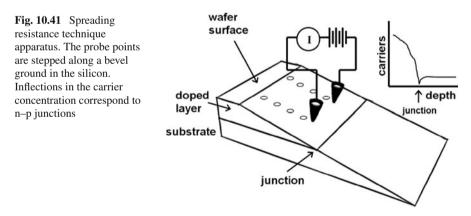

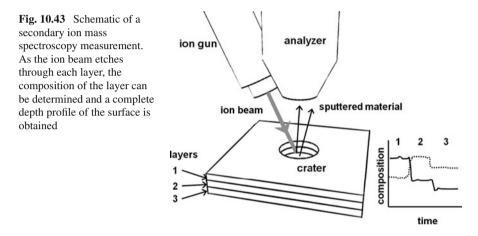

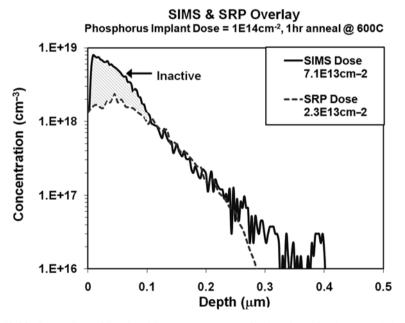

| 10 |                     |          |                                                       |

| 10 | <b>Dopi</b><br>10.1 | -        | esses for MEMS                                        |

|    | 10.1                |          |                                                       |

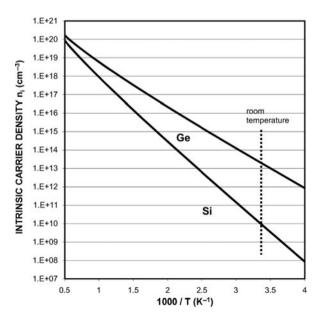

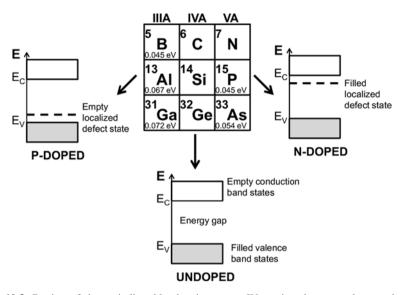

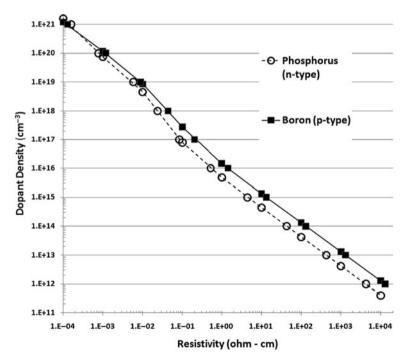

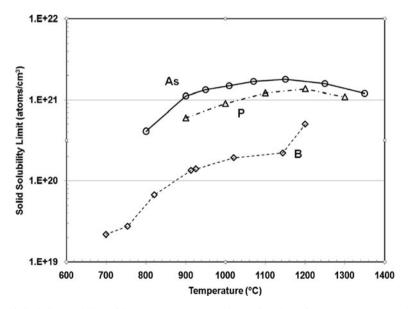

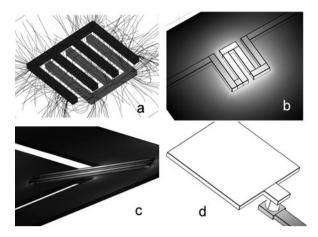

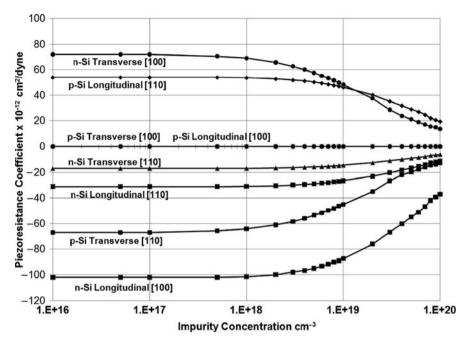

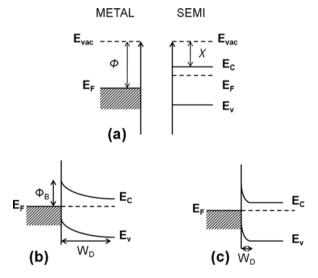

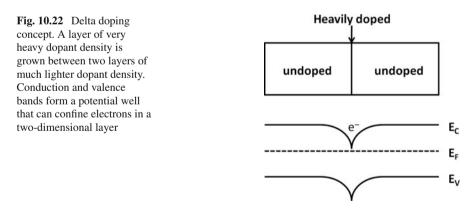

|    | 10.2                | 10.2.1   | ations    756      Electrical Properties    756       |

|    |                     | 10.2.1   | Etch Stop Techniques                                  |

|    |                     | 10.2.2   | Materials and Process Selection Guidelines:           |

|    |                     | 10.2.5   | Etch Stop Techniques                                  |

|    | 10.3                | In Situ  | Doping                                                |

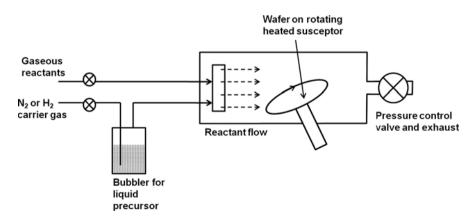

|    | 10.5                | 10.3.1   | Chemical Vapor Deposition                             |

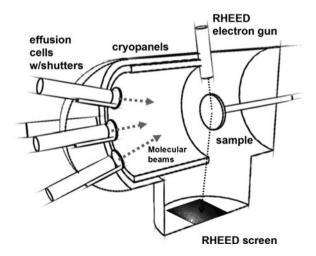

|    |                     | 10.3.1   | Crystal Growth and Epitaxy                            |

|    | 10.4                | Diffusio | 5 1 5                                                 |

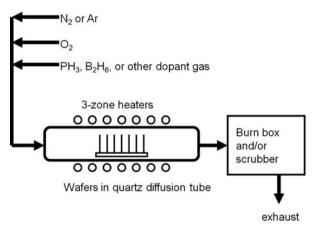

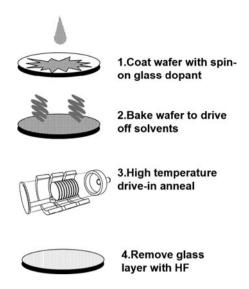

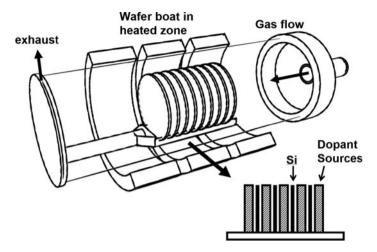

|    | 10.4                | 10.4.1   | Gas Phase Diffusion                                   |

|    |                     | 10.4.1   | Solid State Diffusion                                 |

|    |                     | 10.4.2   | Masking Materials                                     |

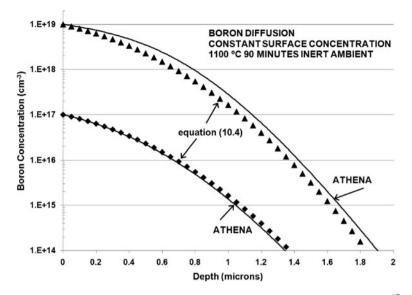

|    |                     | 10.4.4   | Modeling                                              |

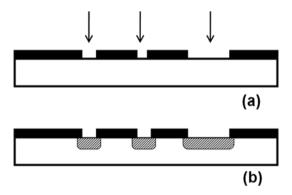

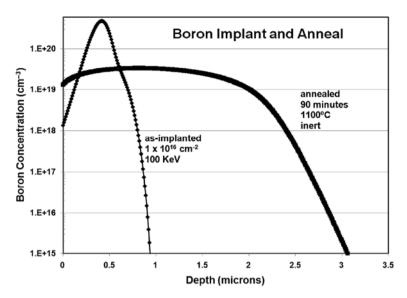

|    | 10.5                |          | plantation                                            |

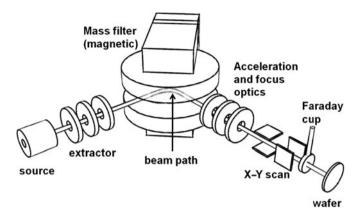

|    | 10.0                | 10.5.1   | Equipment                                             |

|    |                     | 10.5.2   | Masking Materials                                     |

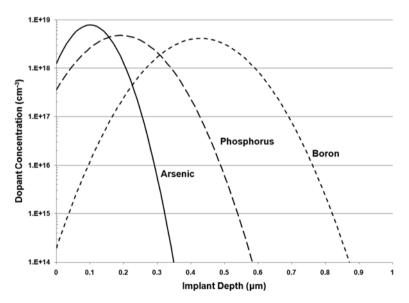

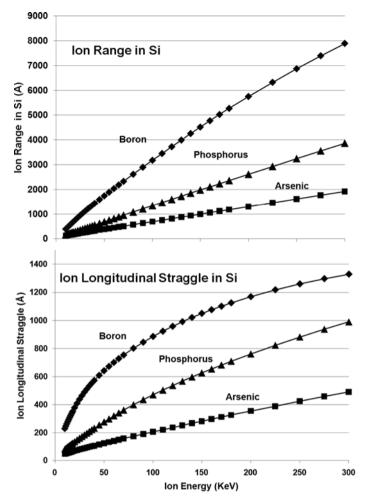

|    |                     | 10.5.3   | Modeling                                              |

|    |                     | 10.5.4   | Crystal Damage                                        |

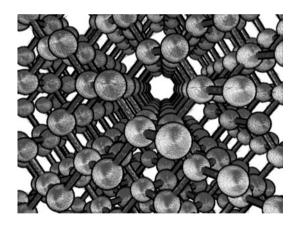

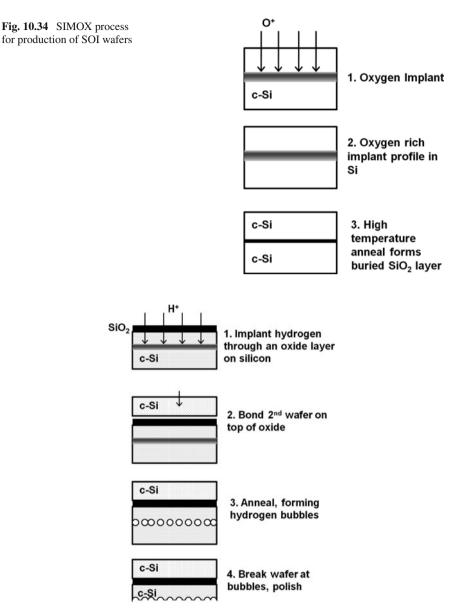

|    |                     | 10.5.5   | Buried Insulator Layers                               |

|    |                     | 10.5.6   | Case Study: Heavily Doped Polysilicon                 |

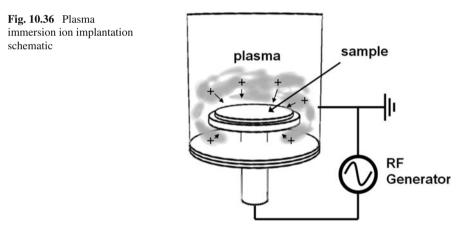

|    | 10.6                | Plasma   | Doping Processes                                      |

|    | 10.7                |          | Activation Methods                                    |

|    |                     | 10.7.1   | Conventional Annealing Methods 800                    |

|    |                     | 10.7.2   | Rapid Thermal Processes                               |

|    |                     | 10.7.3   | Low-Temperature Activation                            |

|    |                     | 10.7.4   | Process Selection Guide: Dopant Activation 803        |

|    |                     | 10.7.5   | Case Study: Rapid Thermal Anneal Versus               |

|    |                     |          | Conventional Thermal Anneal                           |

|    | 10.8                | Diagno   |                                                       |

|    |                     | 10.8.1   | Electrical Measurements                               |

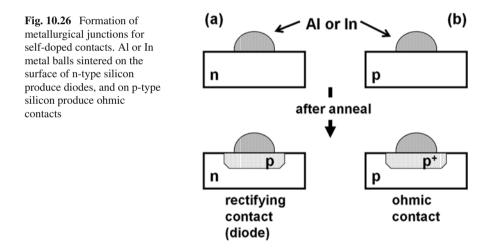

|    |                     | 10.8.2   | Junction Staining Techniques                          |

|    |                     | 10.8.3   | SIMS                                                  |

|    |                     | 10.8.4   | Case Study: Characterizing Junctions and              |

|    |                     |          | Diagnosing Implant Anomalies                          |

|    | Refer               | ences .  |                                                       |

| 11 | Wafe                | r Bondiı | ng                                                    |

|    | 11.1                |          | ction                                                 |

|    | 11.2                |          | Wafer Bonding         821                             |

|    |                     | 11.2.1   | Background and Physics                                |

12

|       | 11.2.2   | Parameter     | s for Successful Direct Wafer Bonding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 824 |

|-------|----------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|